# FS45/FS65 FAQ

# Frequently Asked Questions v2.0

MAY 2021

**CONFIDENTIAL & PROPRIETARY**

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2021 NXP B.V.

NXP INTERNAL USAGE

### NXP CONFIDENTIAL

**NXP Confidential** information is information that may not be publicly disclosed. Unauthorized use and/or disclosure could have limited negative impact on NXP or its staff.

This file is NXP Confidential Information, and it is NXP internal usage. It is protected under NXP Confidential policy.

# CATALOG OVERVIEW

| <u>FS45\FS65 Overview3</u>                    |

|-----------------------------------------------|

| FS45\FS65 part number selection Guide5        |

| Schematic Check List7                         |

| FS45/FS65 Power Management Questions9         |

| FS45/FS65 System Function Questions20         |

| FS45/FS65 State Machine and Modes Questions30 |

| FS45/FS65 Safety Functions Questions36        |

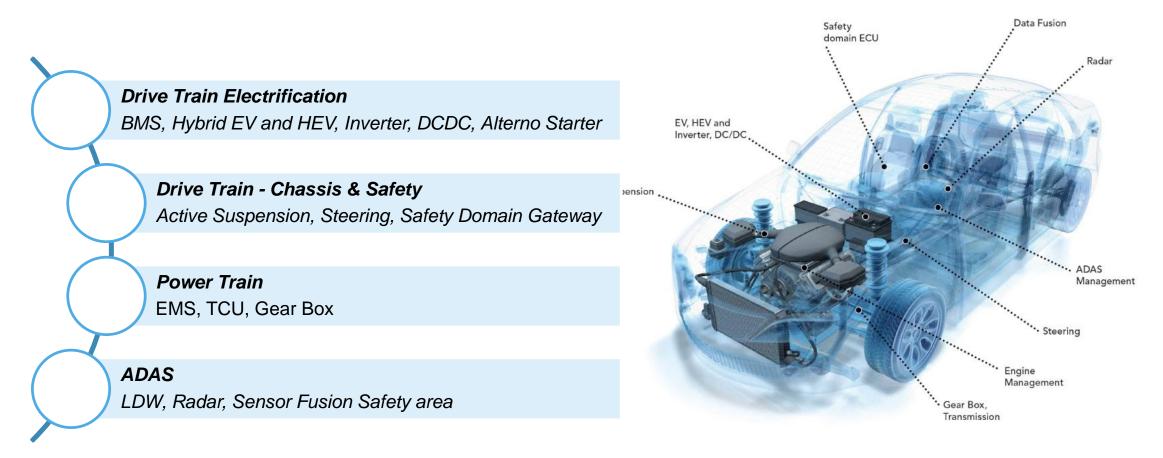

### WHAT APPLICATION FS45/FS65 CAN BE USED ?

FS4500/FS6500 Application in Automotive

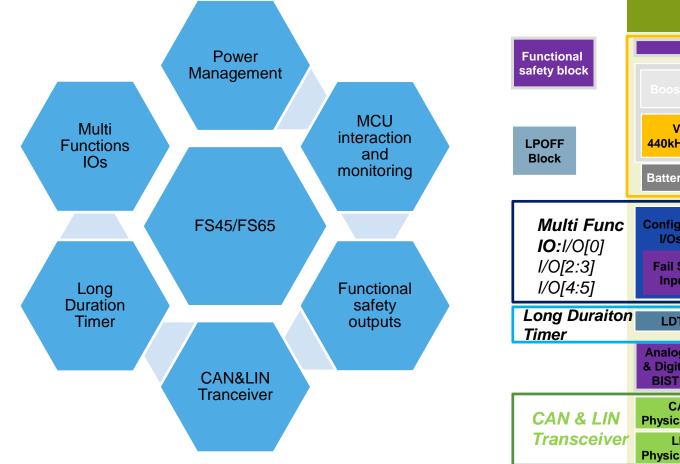

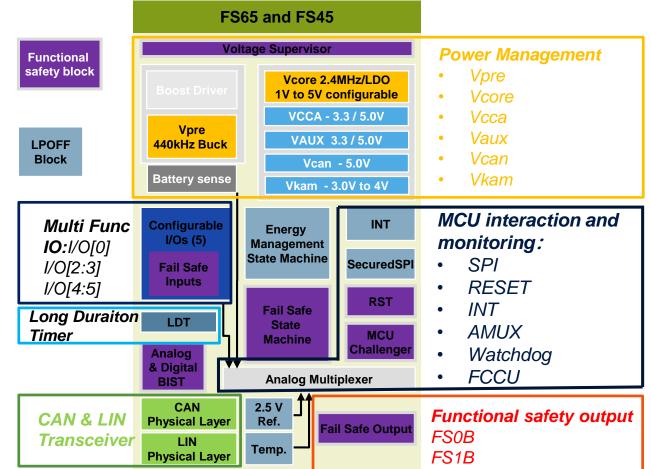

## FS45/FS65 OVERVIEW FUNCTION

FS4500/FS6500 Main Function Blocks

NP

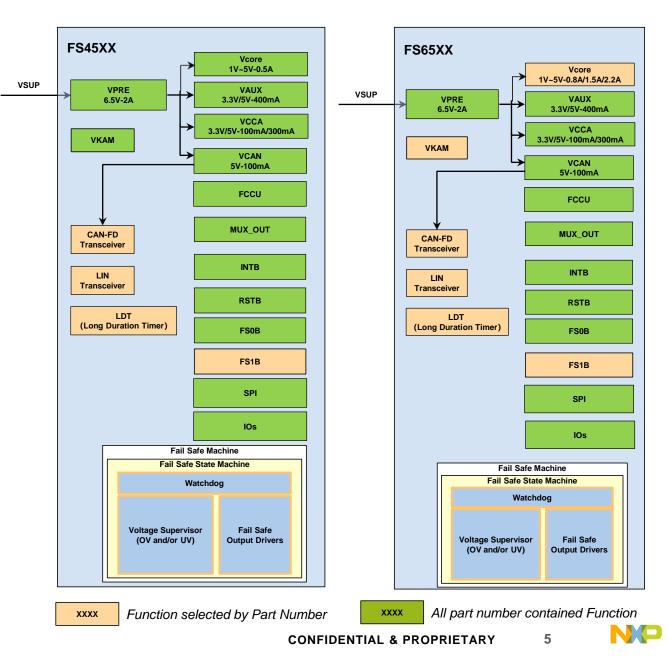

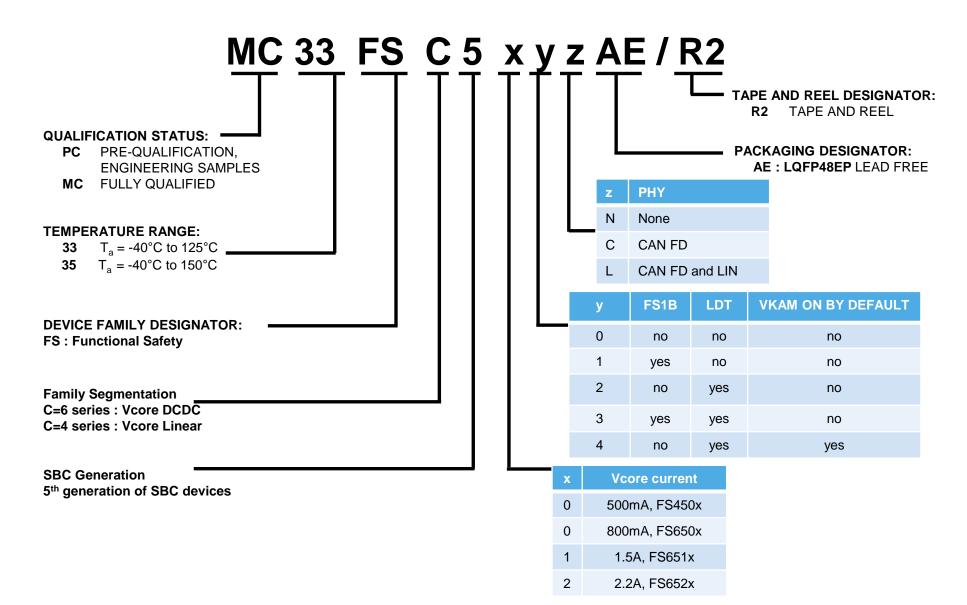

### HOW TO SELECT FS45/FS65 PART NUMBER ?

- FS45XX Vcore is Linear Regulator with 0.5A capability;

- FS65XX Vcore is Buck with 0.8A/1.5A/2.2A Selectable;

### FS45xx Part:

- (1) CAN Transceiver: Part number decide exist or not;

- (2) LIN Transceiver: Part number decide exist or not;

- (3) LDT: Part number decide exist or not;

- (4) FS1B: Part number decide exist or not;

### FS65xx Part:

- (1) Vcore Current Capability: Part number decide 0.8A/1.5A/2.2A

- (2) CAN Transceiver: Part number decide exist or not;

- (3) LIN Transceiver: Part number decide exist or not;

- (4) LDT: Part number decide exist or not;

- (5) FS1B: Part number decide exist or not;

- (6) VKAM: Part number decide ON by default or ON by SPI;

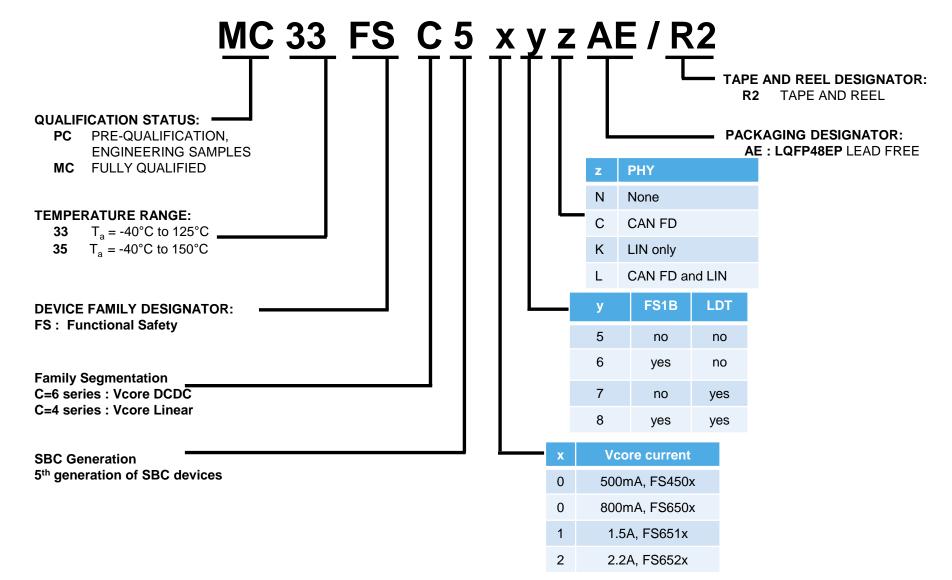

### HOW TO SELECT FS45/FS65(ASIL D) PART NUMBER ?

### HOW TO SELECT FS45/FS65(ASIL B) PART NUMBER ?

7

# FS45/FS65(ASIL D) RECOMMENDED APPLICATION CIRCUIT & SCHEMATIC CHECK-LIST

\* Please refer to Page 133 in Datasheet V7.0 for Figure 73. FS6500 simplified application schematic with CAN, FS1B, VKAM, buck/boost VPRE configuration.

Please refer to Page 134 in Datasheet V7.0 for Figure 74. FS4500 simplified application schematic with CAN, LIN, IO\_5, buck only VPRE configuration.

| Name            | PIN | <i>I/O</i> | Description                  | Recommended Connection                                                                                                                                                                                                                                                                                 | Not Used Features                                                                                                |

|-----------------|-----|------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Vsup1/<br>Vsup2 | 1/2 | Ι          | Device Input pins            | <ul> <li>Reverse Protection between battery and Vsup pins, Pi filter inductor selection: L≤2.2uH</li> <li>Input capacitor should be placed close to Vsup1/2 pins.</li> </ul>                                                                                                                           | N/A                                                                                                              |

| Vsense          | 3   | 1          | Battery Sense                | <ul> <li>Vsense pin connect to battery(prior to reverse protection diode)</li> <li>5.1KΩ series resistor/1uF capacitor to ensure AMUX output accuracy and ISO7637 Robust</li> </ul>                                                                                                                    | N/A                                                                                                              |

| Vsup3           | 4   | 1          | Input pin                    | <ul> <li>Vsup3 pin connected prior to PI filter</li> <li>Input capacitor should be placed close to Vsup3 pin.</li> </ul>                                                                                                                                                                               | N/A                                                                                                              |

| LIN/<br>FS1B    | 5   | I/O        | LIN or FS1B                  | <ul> <li>LIN and FS1B functions are exclusive. When used as FS1B, pull up to VPU_FS</li> <li>FS1B: 5.1KΩ series resistor used to against ISO 7637-2</li> <li>FS1B: 22nF capacitor used to robust against ESD GUN test up to ±8kV, please place this capacitor close to FS1B pin.</li> </ul>            | Floating                                                                                                         |

| IO_4            | 10  | I/O        | Multi Function IO            | <ul> <li>When used as Digital input(Wake up capability), external 5.1KΩ resistor &amp; 470nF capacitor for ISO 7637-2 Robust.</li> <li>Input current within -5mA~5mA;</li> </ul>                                                                                                                       | 5.1KΩ resistor pull down to GND                                                                                  |

| IO5/<br>VKAM    | 11  | I/O        | Multi Function IO            | <ul> <li>When used as Digital input(Wake up capability), external 5.1KΩ resistor &amp; 470nF capacitor for ISO 7637-2 Robust.</li> <li>Input current within -5mA~5mA;</li> <li>If used as VKAM function, 220nF capacitor is needed. For MC33FS6504LAE MC33FS6514LAE, VKAM is ON by default.</li> </ul> | <ul> <li>5.1KΩ resistor pull down to<br/>GND</li> <li>220nF capacitor for VKAM ON<br/>by default part</li> </ul> |

| IO_0            | 12  | I/O        | Multi Function IO            | <ul> <li>Wake up pin for DFS mode, usually connect to KL15/wake up sources. external 5.1KΩ resistor &amp; 470nF capacitor for ISO 7637-2 Robust.</li> <li>Input current within -5mA~5mA;</li> </ul>                                                                                                    | External pull down to GND (Deep<br>fail-safe should be disabled -<br>SELECT pin connected to VPRE)               |

| FCRBM           | 13  | Ι          | Vcore resistor<br>monitoring | This pin is used to monitor the middle point of a redundant resistor bridge connected on VCORE                                                                                                                                                                                                         | If not used, this pin must be<br>connected directly to FB_CORE                                                   |

# FS45/FS65(ASIL D) RECOMMENDED APPLICATION CIRCUIT & SCHEMATIC CHECK-LIST

| Name                       | PIN      | I/O | Description                 | Recommended Connection                                                                                                                                                                                                                                                                                                                      | Not Used Features                           |

|----------------------------|----------|-----|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| FS0B                       | 14       | 0   | Functional safety<br>output | <ul> <li>5.1KΩ Pull up to VDDIO</li> <li>5.1KΩ series resistor used for ISO 7637-2:2011 Robust.</li> <li>22nF capacitor used to robust against ESD GUN test up to ±8kV, place this capacitor close to FS0B pin.</li> </ul>                                                                                                                  | Floating                                    |

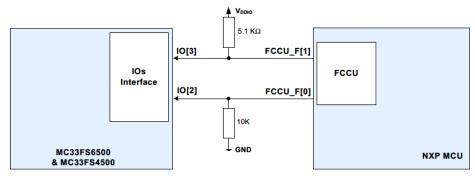

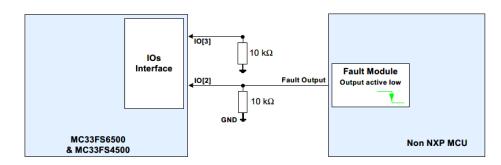

| 102                        | 18       | I   | Multi Function IO           | <ul> <li>When used as FCCU function, 10KΩ pull down to GND, connect to MCU FCCU_F[0]( require output High when MCU is normal and PS=0)</li> <li>When Cooperate with Aurix MCU SMU, 10KΩ pull down to GND and IO2 connect to SMUFSP Pin;</li> <li>When used as Digital input for wakeup capability, IO2 voltage cannot exceed 8V;</li> </ul> | Open/ 5.1KΩ<br>resistor pull down<br>to GND |

| 103                        | 19       | I   | Multi Function IO           | <ul> <li>When used as FCCU function, 5.1KΩ pull up to VDDIO, connect to MCU FCCU_F[1](require output Low when MCU is normal and PS=0)</li> <li>When Cooperate with Aurix MCU SMU, 10KΩ pull down to GND;</li> <li>When used as Digital input for wakeup capability, IO3 voltage cannot exceed 8V;</li> </ul>                                | Open/ 5.1KΩ<br>resistor pull down<br>to GND |

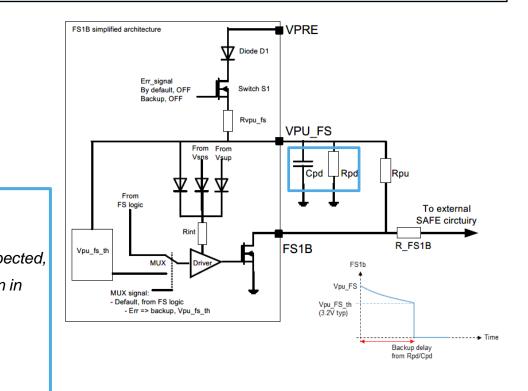

| VPU_FS                     | 22       | 0   | Pull up for FS1B            | Rpd and Cpd connected to this pin will determine back up delay time of FS1B.                                                                                                                                                                                                                                                                | Open                                        |

| RSTB                       | 24       | I/O | Reset                       | <ul> <li>RSTB is OD internal, need 5.1KΩ pull up to VDDIO.</li> <li>1.0nF capacitor used to robust against ESD GUN test up to ±8kV, place this capacitor close to RSTB pin.</li> <li>RSTB is connect to MCU Reset</li> </ul>                                                                                                                | N/A                                         |

| INTB                       | 29       | 0   | Interrupt                   | Internal pull up to VDDIO, no need external Pull up source.                                                                                                                                                                                                                                                                                 | Open                                        |

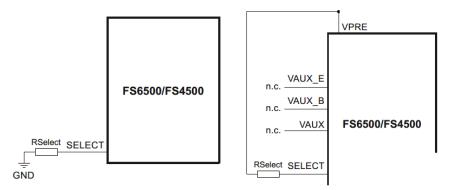

| Select                     | 31       | 1   | Configuration pin           | <ul> <li>Resistor value in select pin determines Vcca / Vaux voltage.</li> <li>Pull down to GND through resistor (Deep Fail Safe enabled); pull up to Vpre through resistor (DFS disabled)</li> </ul>                                                                                                                                       | N/A                                         |

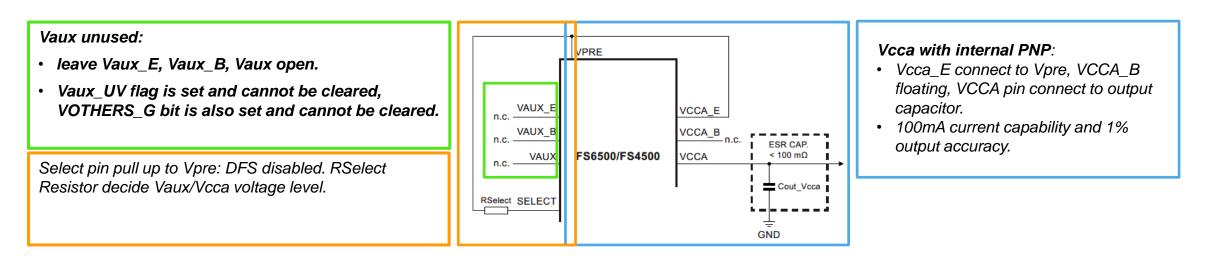

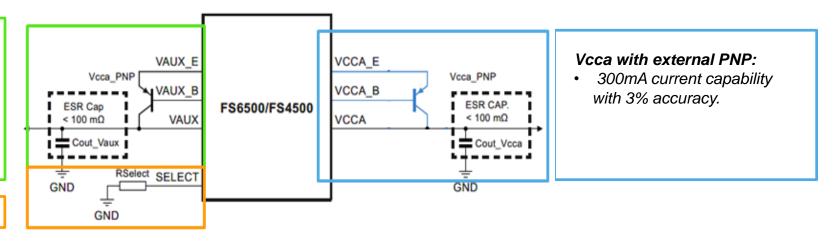

| Vaux,<br>Vaux_E,<br>Vaux_B | 38,39,40 | I/O | Vaux Regulator              | <ul> <li>When Vaux used, must connect external PNP</li> <li>Vaux connect to PNP-C and output capacitor, Vaux_B connect to PNP-B, Vaux_E connect to PNP-E.</li> <li>Vaux output capacitor voltage tolerance should be&gt;40V when Vaux is used as off board power supply</li> </ul>                                                          | VAUX Open,<br>Vaux_E Open,<br>Vaux_B Open   |

| Vcca,<br>Vcca_E,<br>Vcca_B | 41,42,43 | I/O | Vcca Regulator              | <ul> <li>When external PNP used, Vcca connect to PNP-C and output capacitor, Vcca_B connect to PNP-B, Vcca_E connect to PNP-E.</li> <li>When internal PNP used, Vcca connect to output capacitor, Vcca_E connect to Vpre, Vcca_B open.</li> </ul>                                                                                           | N/A                                         |

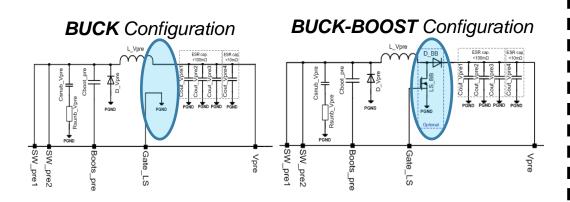

| GATE_LS                    | 44       | 0   | Gate Driver                 | <ul> <li>When GATE_LS pin connect to GND, Vpre is configured as Buck Mode;</li> <li>When GATE_LS pin connect to Gate of MOS, Vpre is configured as Buck-Boost Mode,</li> </ul>                                                                                                                                                              | N/A                                         |

### FS45/FS65 POWER MANAGEMENT

### QUESTIONS

- **Vsup:** <u>What's the Input range of the device and Work State ?</u>

- **Vsup:** <u>What's the function of Pi filter, how to select components for VSUP/Vsense ?</u>

- Vpre: <u>How to configure Buck only/ Buck-Boost Mode and how to design Vpre external circuits?</u>

- Vcore: <u>How to design Vcore external circuits and how to use FCRBM function?</u>

- Vcca/Vaux: What's vaux connection when used or unused?

- Vcca/Vaux: <u>What's Vcca connection when 100mA/300mA current capability?</u>

- Vcca/Vaux: <u>How to configure VCCA/VAUX voltage level?</u>

- Vcca/Vaux: <u>How to use Tracker Mode and what's the advantage?</u>

- Vcca/Vaux: What's the behavior of Vcca/Vaux when overcurrent happen and how to recovery ?

- Vcore/Vcca/Vaux: What's degrade mode and how to configure it?

- Vkam: What's Vkam, how to configure Vkam?

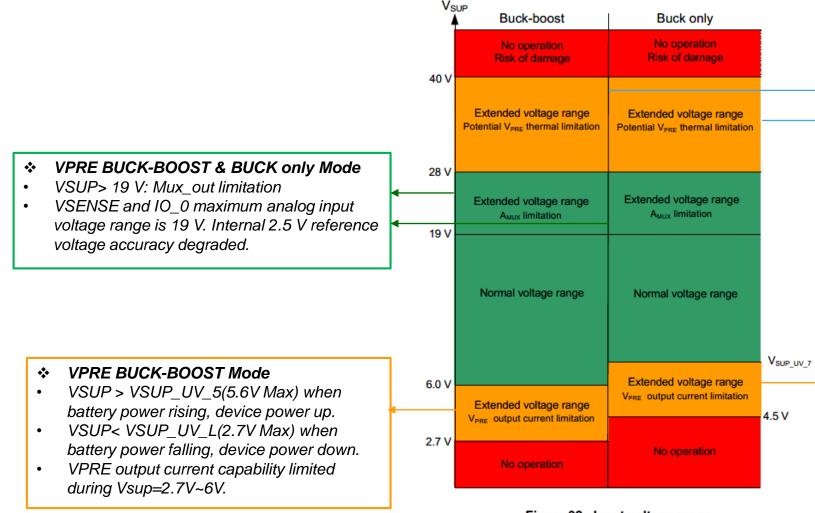

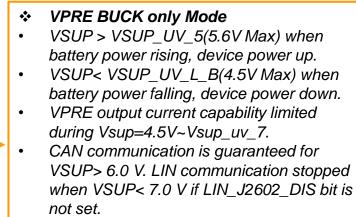

### VSUP: WHAT'S THE INPUT RANGE OF THE DEVICE AND WORK STATE ?

VPRE BUCK-BOOST & BUCK only Mode VSUP > 28 V: Potential VPRE thermal limitation RDS(on), Current limitation and overcurrent detection are specified for VSUP< 28 V.</p>

For VCCA and VAUX, 5.0 V configuration, undervoltage triggers at low VSUP(refer to VCCA\_UV\_5 and VAUX\_UV\_5)

*Note: If only Vsup > VSUP\_UV\_5(5.6V Max), Device will power on, regardless of IO pins state.*

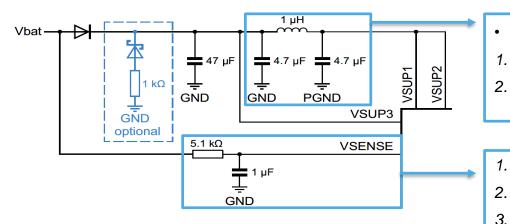

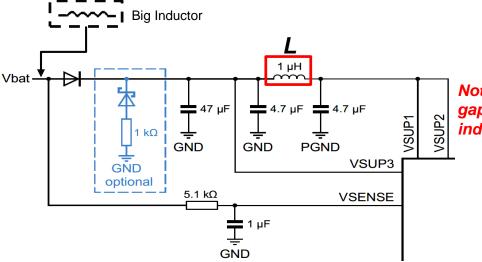

### VSUP: WHAT'S THE FUNCTION OF PI FILTER, HOW TO SELECT COMPONENTS FOR VSUP/VSENSE ?

#### PI Filter Function:

- PI filter will filter the noise from Vbat to Vsup1/2, avoid the noise impaction on SMPS.

- 2. PI filter will filter the noise from VSUP1/2(SMPS) to Vsup3, avoid SMPS noise impaction on Vsup3.

- 1. A big capacitor >47uF is needed before Vsup3 for VBATT oscillation Robust.

- 2. Vsense pin should connect prior to Reverse Protection circuit, so that sense battery voltage.

- 3. Vsense pin can stand -14V~40V voltage.

- 4. 5.1KΩ resistor should NOT be changed, otherwise it will impact on AMUX output accuracy.

Note: Datasheet says, Vsup1/2 and Vsup3 should be the same power, so L<2.2uH to avoid voltage gap between Vsup1/2 and Vsup3 created when battery voltage oscillation. If needed, another inductor before FS45/FS65 for the whole board with a bigger value to help the EMC Performance.

### VPRE: HOW TO CONFIGURE BUCK ONLY/ BUCK-BOOST MODE AND HOW TO DESIGN VPRE EXTERNAL CIRCUITS?

• Vpre mode is automatically detected when Power up and wake up from LPOFF mode.

• After device power up, Vpre mode can be known by reading LS\_DETECT bit in HW\_CONFIG register.

#### Table 34. HW\_CONFIG register description

| Read |       |       |       |       |       |       |       |         |        |      |         |       |       |      |         |        |

|------|-------|-------|-------|-------|-------|-------|-------|---------|--------|------|---------|-------|-------|------|---------|--------|

|      | bit15 | bit14 | bit13 | bit12 | bit11 | bit10 | bit9  | bit8    | bit7   | bit6 | bit5    | bit4  | bit3  | bit2 | bit1    | bit0   |

| MOSI | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0       | 0      | 0    | 0       | 0     | 0     | 0    | 0       | 0      |

|      |       |       |       |       |       |       |       |         |        |      |         |       |       |      |         |        |

| MISO | SPI_G | WU_G  | CAN_G | LIN_G | IO_G  | VPRE  | VCORE | VOTHERS | LS_    |      |         | VCCA_ | VAUX_ | 1    | DFS_HW1 | DBG_HW |

|      |       |       |       |       |       | _G    | _G    | G       | DETECT | ED   | PNP_DET | HW    | нw    |      |         |        |

#### Table 35. HW\_CONFIG description and configuration of the bits (default value in bold)

|           | Description     | Report the hardware configuration of VPRE |

|-----------|-----------------|-------------------------------------------|

| LS DETECT | 0               | Buck-boost                                |

| L3_DETECT | 1               | Buck only                                 |

|           | Reset condition | Power on reset/refresh after LPOFF        |

|           | Reset condition | Power on reset/refresh after LPOFF        |

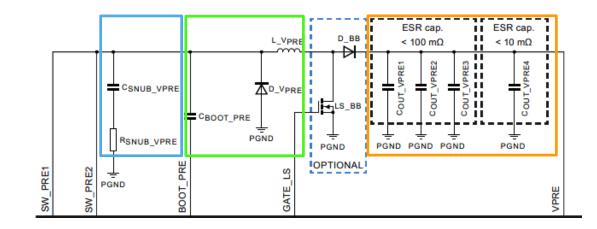

### Snubber for emission reduction:

- Filter ripple at turn ON

- Values depends of PCB layout performance and should be fine tuned

- Resistor power dissipation must be bigger than 1/4W.

- Csnub\_pre usually <2.2nF, Rsnub\_vpre usually ~10ohm from experience, and the Values depends on SW\_PRE waveform. Big capacitor will lead to loss of Vpre efficiency .

#### Bootstrap capacitor: 100nF

- Provide High side gate drive at Vsup +10V,440KHZ switching frequency

- Not Recommended to add resister between CBOOT\_PRE and BOOT\_PRE pin.

#### Output filtering capacitor :

- Ceramic capacitor with low ESR. Minimum 40µF recommended.

- Low ESR <10mohms at resonance frequency.

- Voltage rating > 2x max output voltage (16V)

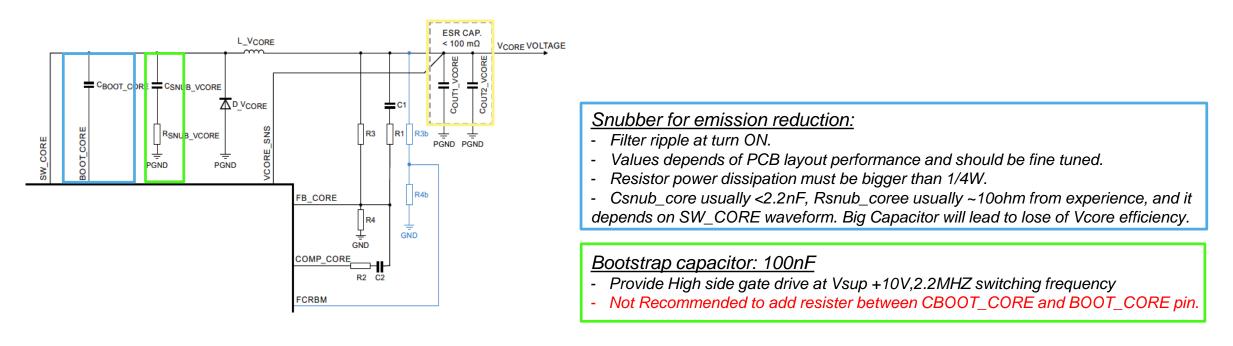

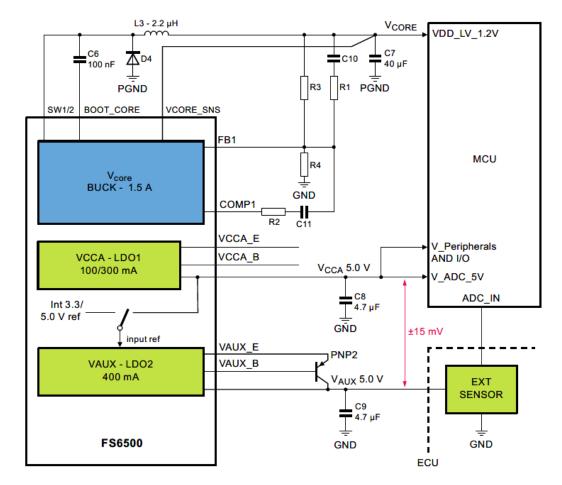

### VCORE: HOW TO DESIGN VCORE EXTERNAL CIRCUITS AND HOW TO USE FCRBM FUNCTION.

- Ceramic output filtering capacitor from 20uF to 40uF depending on output current capability (low ESR)

- FB\_CORE is always regulated at 0.8V and Vcore voltage Configurable from 1V to 5V range is setup by the external resistor bridge R3/R4 (+/-1%).

- FCRBM pin connect to the same resistor bridge with FB\_CORE pin, when | FCRBM-FB\_CORE | > 150mV, FCRBM\_OV, FCRBM\_UV Triggered; this function is

used for Vcore external resistors(R3,R4) drift monitoring.

- FCRBM\_OV, FCRBM\_UV Impact configuration is same with VCORE\_FB\_OV, VCORE\_FB\_UV impact configuration(in INIT\_VCORE\_OVUV\_IMPACT register)

- If R3b, R4b/FCRBM are not used, FCRBM pin should connect to FB\_CORE pin.

# VCCA/VAUX: WHAT'S VAUX CONNECTION WHEN USED OR UNUSED? WHAT'S VCCA CONNECTION WHEN 100MA/300MA CURRENT CAPABILITY

Vaux used: 400mA current capability.

- Vaux pin can stand 40V max, so it can be used as off boards power supply.

- Output capacitor: Min 4.7uF, 50V voltage tolerance when used as offboard power supply, as it is possible short to battery.

Select pin pull down to GND: DFS enabled

Note: Vaux can be used or unused, but Vcca must be used with internal PNP or external PNP Connection.

### VCCA/VAUX: HOW TO CONFIGURE VCCA/VAUX VOLTAGE LEVEL

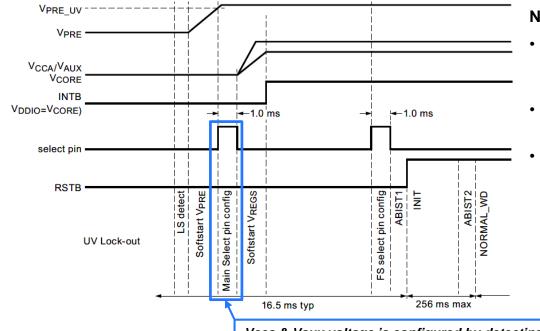

Vcca & Vaux output voltage are only decided by Rselect value as shown in below picture. No matter resistor connect to GND or Vpre.

| Vcca  | Vaux  | Rselect (kΩ) | Recommended Value |

|-------|-------|--------------|-------------------|

| 3.3 V | 3.3 V | < 6          | 5.1 kΩ ± 5 %      |

| 5 V   | 5 V   | 10.8 << 13.2 | 12 kΩ ± 5 %       |

| 3.3 V | 5 V   | 21.6 << 26.4 | 24 kΩ ± 5 %       |

| 5 V   | 3.3 V | 45.9 << 56.1 | 51 kΩ ± 5 %       |

Vcca & Vaux voltage is recognized once by reading resistor value in Main select pin configure phase.

#### NOTE:

- If Rselect resistor value change after **Main Select pin config phase**, Vcca & Vaux voltage will not change and still output as detected in Main Select pin config phase.

- *If Rselect open, or short, or out of resistance ranges when detected in Main Select pin config phase. Both Vcca & Vaux will output 3.3V.*

- Vcca & Vaux voltage level detection result can be SPI read in HW\_CONFIG register, VCCA\_HW and VAUX\_HW bits.

Vcca & Vaux voltage is configured by detecting Rselect value in this phase.

NC

### VCCA/VAUX: HOW TO USE TRACKER AND WHAT'S THE ADVANTAGE?

#### Vaux Tracker Mode Application:

- 1. Vcca and Vaux are the same voltage level.

- 2. Vcca supply for ADC reference and Vaux supply for Ext Sensor.

### Advantage:

- 1. Vaux can track Vcca voltage and keep ±15mV accuracy, will help to achieve high ADC sample accuracy.

- 2. Vaux pin can stand 40V DC Max, which protect pins in case battery short to Vaux through cable, so it is suitable for off boards power supply.

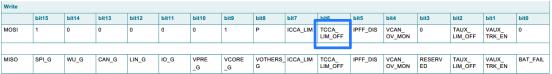

#### How to configure Vaux as Tracker Mode

- 1. Vaux is no tacking by default.

- 2. Tracker mode is enable by SPI writing VAUX\_TRK\_EN =1 in INIT\_VREG Register(only can be Written in INIT Mode)

|             | Description     | Configure VAUX regulator as a tracker of VCCA |

|-------------|-----------------|-----------------------------------------------|

| VAUX TRK EN | 0               | NO tracking.                                  |

| VAUX_TRK_EN | 1               | Tracking mode enabled and latched             |

|             | Reset condition | Power on reset                                |

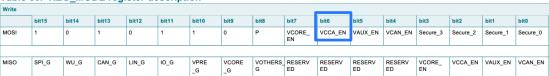

#### Table 22. INIT\_VREG register description

|       |       | -     | -     |       |       |            |             |               |          |                  |          |                 |              |                  |                 |          |

|-------|-------|-------|-------|-------|-------|------------|-------------|---------------|----------|------------------|----------|-----------------|--------------|------------------|-----------------|----------|

| Write |       |       | -     |       |       | -          |             |               |          |                  |          |                 |              |                  | -               |          |

|       | bit15 | bit14 | bit13 | bit12 | bit11 | bit10      | bit9        | bit8          | bit7     | bit6             | bit5     | bit4            | bit3         | bit2             | bit1            | bit0     |

| MOSI  | 1     | 0     | 0     | 0     | 0     | 0          | 1           | Ρ             | ICCA_LIM | TCCA_<br>LIM_OFF | IPFF_DIS | VCAN_<br>OV_MON | 0            | TAUX_<br>LIM_OFF | VAUX_<br>TRK_EN | 0        |

|       |       |       |       |       |       |            |             |               |          |                  |          |                 |              |                  |                 |          |

| MISO  | SPI_G | WU_G  | CAN_G | LIN_G | IO_G  | VPRE<br>_G | VCORE<br>_G | VOTHERS_<br>G | ICCA_LIM | TCCA_<br>LIM_OFF | IPFF_DIS | VCAN_<br>OV_MON | RESERV<br>ED | TAUX_<br>LIM_OFF | VAUX_<br>TRK_EN | BAT_FAIL |

NP

**Vaux output Current Limit:** A current limitation is implemented to avoid uncontrolled power dissipation of the external PNP transistor. The current is limited to IAUX\_LIM and the regulator is switch off after a dedicated duration tAUX\_LIM\_OFF under current limitation.

| I <sub>AUX_OUT</sub>                                   | V <sub>AUX</sub> output current                        | _        | _ | 400      | mA |

|--------------------------------------------------------|--------------------------------------------------------|----------|---|----------|----|

| I <sub>AUX_LIM</sub>                                   | V <sub>AUX</sub> output current limitation             | 400      | — | 800      | mA |

| AUX_LIM_FB                                             | V <sub>AUX</sub> output current limitation foldback    | 60       | — | 240      | mA |

| V <sub>AUX_LIM_FB</sub>                                | V <sub>AUX</sub> output voltage foldback threshold     | 0.6      | - | 1.2      | V  |

| t <sub>AUX_LIM</sub>                                   | V <sub>AUX</sub> output current limitation filter time | 1.0      | _ | 3.0      | μs |

| t <sub>AUX_LIM_OFF1</sub><br>t <sub>AUX_LIM_OFF2</sub> | V <sub>AUX</sub> output current limitation duration    | 10<br>50 |   | 15<br>60 | ms |

Vaux\_LIM\_OFF (50ms by default) is selected in INIT\_VREG register.

| Write |       |       |       |       |       |            |             |              |          |                  |          |                 |              |                  |                 |         |

|-------|-------|-------|-------|-------|-------|------------|-------------|--------------|----------|------------------|----------|-----------------|--------------|------------------|-----------------|---------|

|       | bit15 | bit14 | bit13 | bit12 | bit11 | bit10      | bit9        | bit8         | bit7     | bit6             | bit5     | bit4            | bit3         | bit2             | bit1            | bit0    |

| MOSI  | 1     | 0     | 0     | 0     | 0     | 0          | 1           | Р            | ICCA_LIM | TCCA_<br>LIM_OFF | IPFF_DIS | VCAN_<br>OV_MON | 0            | TAUX_<br>LIM_OFF | VAUX_<br>TRK_EN | 0       |

|       |       |       |       |       |       |            |             |              |          |                  |          |                 |              |                  |                 |         |

| MISO  | SPI_G | WU_G  | CAN_G | LIN_G | IO_G  | VPRE<br>_G | VCORE<br>_G | VOTHERS<br>G | ICCA_LIM | TCCA_<br>LIM_OFF | IPFF_DIS | VCAN_<br>OV_MON | RESERV<br>ED | TAUX_<br>LIM_OFF | VAUX_<br>TRK_EN | BAT_FAI |

*Vaux is shut down and cannot recover* when Vaux output current reach current limit even if Vaux overcurrent removed. Vaux can be enabled by SPI writing "Vaux\_EN=1" in REG\_MODE Register.

####

Vcca output Current Limit:

Vcca use external PNP: Vcca current limit protection mechanism is the same with Vaux. Vcca shut down when output current reach current limitation and will not recover when overcurrent removed. Vcca can be enabled by SPI writing "Vcca\_EN=1" in REG\_MODE Register.

| ICCA_LIM_INT                                           | V <sub>CCA</sub> output current limitation (int. MOSFET)  |          | 1( | 00 | —        | 675 | mA |

|--------------------------------------------------------|-----------------------------------------------------------|----------|----|----|----------|-----|----|

| ICCA_LIM_OUT                                           | V <sub>CCA</sub> output current limitation (external PNP) |          | 30 | 00 | —        | 675 | mA |

| ICCA_LIM_FB                                            | V <sub>CCA</sub> output current limitation foldback       |          | 6  | 0  | —        | 240 | mA |

| V <sub>CCA_LIM_FB</sub>                                | V <sub>CCA</sub> output voltage foldback threshold        |          | 0  | .6 | —        | 1.2 | V  |

| t <sub>CCA_LIM</sub>                                   | V <sub>CCA</sub> output current limitation filter time    | 1.       | 0  | _  | 3.0      | μs  |    |

| t <sub>CCA_LIM_OFF1</sub><br>t <sub>CCA_LIM_OFF2</sub> | V <sub>CCA</sub> output current limitation duration       | 1)<br>5) |    |    | 15<br>60 | ms  |    |

#### Vcca\_LIM\_OFF (50ms by default) is selected in INIT\_VREG register.

#### Table 22. INIT\_VREG register description

#### Table 60. REG\_MODE register description

• Vcca with internal PNP: Vcca outputs 0 when Vcca output current reach to current limit, Vcca will recover automictically after overcurrent current removed.

| I <sub>CCA_LIM_INT</sub> | V <sub>CCA</sub> output current limitation (int. MOSFET)  | 100 | — | 675 | mA |

|--------------------------|-----------------------------------------------------------|-----|---|-----|----|

| I <sub>CCA_LIM_OUT</sub> | V <sub>CCA</sub> output current limitation (external PNP) | 300 | — | 675 | mA |

| I <sub>CCA_LIM_FB</sub>  | V <sub>CCA</sub> output current limitation foldback       | 60  | _ | 240 | mA |

| V <sub>CCA_LIM_FB</sub>  | V <sub>CCA</sub> output voltage foldback threshold        | 0.6 | — | 1.2 | V  |

### VCORE/VCCA/VAUX: WHAT'S DEGRADE MODE AND HOW TO CONFIGURE IT?

• Vcore, Vcca, Vaux support degrade mode, only valid when they output 5V. Degrade mode has a lower UV voltage threshold.

| V <sub>CCA_UV_5</sub>     |                                                                                                 |      | — | 4.75  | V |

|---------------------------|-------------------------------------------------------------------------------------------------|------|---|-------|---|

| V <sub>CCA_UV_5D</sub>    | $V_{CCA}$ undervoltage detection threshold (degraded 5.0 V)                                     | 3.0  | — | 3.2   | V |

| V <sub>CORE_FB_UV</sub>   | V <sub>CORE</sub> FB undervoltage detection threshold                                           | 0.67 | — | 0.773 | V |

| V <sub>CORE_FB_UV_D</sub> | V <sub>CORE_FB_UV_D</sub> V <sub>CORE</sub> FB undervoltage detection threshold - degraded mode |      | — | 0.58  | V |

| V <sub>AUX_UV_5</sub>     | V <sub>AUX</sub> undervoltage detection threshold (5.0 V configuration)                         | 4.5  | _ | 4.75  | V |

| V <sub>AUX_UV_5D</sub>    | $V_{AUX}$ undervoltage detection threshold (degraded 5.0 V)                                     | 3.0  | — | 3.2   | V |

Vcore, Vcca, Vaux are normal mode by default and degraded mode can be configured by MCU SPI writing INIT\_SUPERVISOR register.

(only can be written in INIT\_FS mode).

Table 80. INIT\_SUPERVISOR register description

| Write |       |       |       |       |       |            |             |              |                |                |                |                     |              |             |             |                     |

|-------|-------|-------|-------|-------|-------|------------|-------------|--------------|----------------|----------------|----------------|---------------------|--------------|-------------|-------------|---------------------|

|       | bit15 | bit14 | bit13 | bit12 | bit11 | bit10      | bit9        | bit8         | bit7           | bit6           | bit5           | bit4                | bit3         | bit2        | bit1        | bit0                |

| MOSI  | 1     | 1     | 0     | 0     | 0     | 1          | 1           | Ρ            | VCORE_<br>5D   | VCCA_5D        |                | FS1B_TIME_<br>RANGE | Secure_3     | Secure_2    | Secure_1    | Secure_0            |

|       |       |       |       |       |       |            |             |              |                |                |                |                     |              |             |             |                     |

| MISO  | SPI_G | WU_G  | CAN_G | LIN_G | IO_G  | VPRE<br>_G | VCORE<br>_G | VOTHERS<br>G | SPI_FS_<br>ERR | SPI_FS_<br>CLK | SPI_FS_<br>REQ | SPI_FS_<br>PARITY   | VCORE_<br>5D | VCCA_<br>5D | VAUX_<br>5D | FS1B_TIME_<br>RANGE |

Note: ABIST2\_Vaux is conducted through MCU SPI command, ABIST2\_VAUX must be conducted before Vaux degraded mode configuration, otherwise, ABIST2\_VAUX will fail.

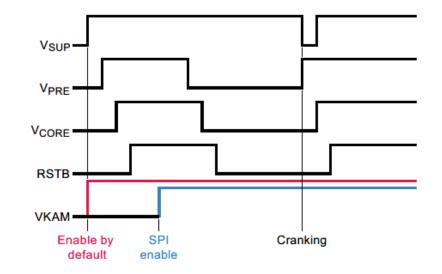

### VKAM: WHAT'S VKAM, HOW TO CONFIGURE VKAM ?

• VKAM is an always ON regulator once it is enabled, no matter in LPOFF or DFS mode(Powered by VSUP3). VKAM spec are shown as below:

| VKAM voltag          | ge regulator                                                                                                                                                                |     |     |                   |                |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------------|----------------|

| V <sub>KAM</sub>     | V <sub>KAM</sub> output voltage                                                                                                                                             | 3.0 | 3.5 | 4.0               | V              |

| I <sub>KAM_OUT</sub> | V <sub>KAM</sub> output current                                                                                                                                             | _   | _   | 3.0               | mA             |

| I <sub>KAM_LIM</sub> | V <sub>KAM</sub> output current limitation                                                                                                                                  | 4.0 | —   | 10.0              | mA             |

| I <sub>SUP_KAM</sub> | V <sub>KAM</sub> current consumption from V <sub>SUP3</sub><br>• I <sub>KAM_OUT</sub> = 0 mA<br>• I <sub>KAM_OUT</sub> < 1.0 mA<br>• 1.0 mA < I <sub>KAM_OUT</sub> < 3.0 mA |     |     | 25<br>150<br>2.15 | μΑ<br>μΑ<br>mA |

• VKAM and IO5 use the same pin, for MC33FS6504LAE(ASIL D) and MC33FS6514LAE(ASIL D), VKAM is ON by default; VKAM should be enabled by

SPI command(VKAM\_EN=1 in Mode Register in Normal Phase) for other FS part numbers.

### **FS45/FS65 SYSTEM FUNCTION**

## QUESTIONS

- > MUX\_OUT: What's MUX OUT and HOW to use MUX OUT ?

- > MUX\_OUT: <u>MUX\_OUT accuracy and how to calibration ?</u>

- > LDT: What is LDT ? How to use LDT? What's LDT accuracy ? How to do calibration ?

- SPI: What's FS45/FS65 SPI prototype ? How to configure the parameter in software?

- ➢ IOs: <u>What function IOO can support and how to use the function ?</u>

- ➢ IOs: What function IO2&IO3 can support and how to use the function ?

- IOs: What function IO4&IO5 can support and how to use the function ?

- CAN: <u>How CANH/CANL short to battery, CANH/CANL short to GND detection?</u>

- CAN: FS45/FS65 CAN PHY work normally in DEBUG mode, but fail after changing to non-DEBUG Mode?

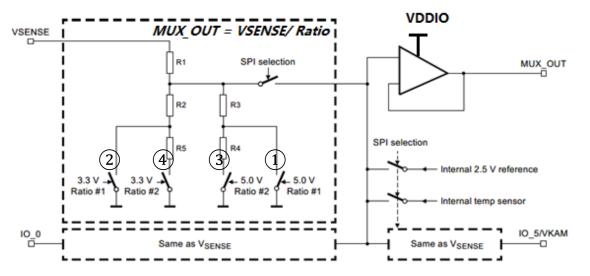

### MUX\_OUT: WHAT'S MUX\_OUT, HOW TO USE MUX\_OUT ? MUX\_OUT ACCURACY AND HOW TO DO CALIBRATION ?

- MUX\_OUT pin delivers analog voltage to the MCU ADC input. Help customer save ADC Sample circuits.

- Monitoring battery voltage from vsense, FS45/FS65 internal temp, and so on. Analog voltage can be selected from Vsense, IO0, IO5/VKAM, Internal 2.5V or Internal temp sensor. MUX Input Channels and Ratios are selected by SPI writing IO\_OUT\_AMUX register AMUX\_2:0 Bits.

### When AMUX\_2:0 select Vsns, IO0, IO5

MUX\_OUT = Vsense/Ratio; Ratio is selected by wide range or tight range.

|          | Description     | Select AMUX output           |  |  |  |  |

|----------|-----------------|------------------------------|--|--|--|--|

|          | 000             | V <sub>REF</sub>             |  |  |  |  |

|          | 001             | V <sub>SNS</sub> wide range  |  |  |  |  |

|          | 010             | IO_0 wide range              |  |  |  |  |

| AMUX_2:0 | 011             | IO_5 wide range              |  |  |  |  |

| AMUX_2:0 | 100             | V <sub>SNS</sub> tight range |  |  |  |  |

|          | 101             | IO_0 tight range             |  |  |  |  |

|          | 110             | IO_5 tight range/VKAM        |  |  |  |  |

|          | 111             | Die Temperature Sensor       |  |  |  |  |

|          | Reset condition | Power on reset               |  |  |  |  |

#### there are both wide ranges/tight ranges @VDDIO=3.3V or VDDIO=5V.

| V <sub>AMUX_TG_5</sub>   | Divider ratio <mark>(tight input voltage range) at V<sub>DDIO</sub> = 5.0 V</mark> | — | 2.0 1 -   |

|--------------------------|------------------------------------------------------------------------------------|---|-----------|

| V <sub>AMUX_TG_3P3</sub> | Divider ratio <mark>(tight input voltage range) at V<sub>DDIO</sub> = 3.3 V</mark> | — | 3.0 (2) - |

| V <sub>AMUX_WD_5</sub>   | Divider ratio (wide input voltage range) at V <sub>DDIO</sub> = 5.0 V              | — | 5.0 (3) - |

| V <sub>AMUX_WD_3P3</sub> | Divider ratio (wide input voltage range) at V <sub>DDIO</sub> = 3.3 V              | — | 7.0 4 -   |

#### **Configuration:**

- When AMUX\_2:0 = 001(Vsns wide range), MUX\_OUT = Vsense/Ratio, Ratio = 5 @ VDDI0=5V, Ratio = 7 @VDDI0=3.3V. MUX\_OUT voltage will not exceed VDDIO.

- When AMUX\_2:0 = 100(Vsns tight range) MUX\_OUT = Vsense/Ratio, Ratio = 2 @ VDDI0=5V, Ratio = 3 @VDDI0=3.3V. MUX\_OUT voltage will not exceed VDDIO.

- Same calculation when AMUX\_2:0 select IO0 analog input, IO5 analog input.

- VSENSE and IO\_0 maximum analog input voltage range is 19 V.

- Serial Resistors(R1,R2,R3,R4,R5) are  $M\Omega$  level.

#### Calibration:

VSENSE voltage can be monitored through the MUX\_OUT pin with **5.0** % accuracy, After calibration, the VSENSE monitoring accuracy can achieve  $\pm 1$ %, for both VDDIO = 3.3 V and 5.0 V, in wide range resistor bridge configuration (without taking into account the VSENSE supply accuracy used for the calibration). Calibration method example:

- Set VBAT1 = 12V, MCU ADC read MUX\_OUT output voltage as Vmux1;

- Set VBAT1 = 14V, MCU ADC read MUX\_OUT output voltage as Vmux2; VBAT1 = A\*Vmux1 + B; VBAT2 = A\*Vmux2 + B;

- get A. B, calculate Vsense voltage by Vsense = A\* Vmux+ B.

NKP

### MUX\_OUT: WHAT'S MUX\_OUT, HOW TO USE MUX\_OUT ? MUX\_OUT ACCURACY AND HOW TO CALIBRATION ?

### • When AMUX\_2:0 select internal 2.5V reference

MUX\_OUT = 2.5V, Internal 2.5 V reference voltage accuracy degraded when VSUP > 19 V.

| V <sub>AMUX_REF1</sub> | Internal voltage Reference with 6.0 V < $V_{SUP}$ < 19 V                                    | 2.475 | 2.5 | 2.525 | V |

|------------------------|---------------------------------------------------------------------------------------------|-------|-----|-------|---|

| V <sub>AMUX_REF2</sub> | Internal voltage reference with $V_{SUP} \le 6.0 \text{ V}$ , or $V_{SUP} \ge 19 \text{ V}$ | 2.468 | 2.5 | 2.532 | V |

#### • When AMUX\_2:0 select internal 2.5V reference

Internal temp sensor, real temperature can be calculated by below formula, VMUX is FS45/FS65 MUX\_OUT voltage read by MCU ADC.

$$T(^{\circ}C) = (V_{AMUX} - V_{AMUX_{TP}})/V_{AMUX_{TP}_{CO}} + 165$$

| V <sub>AM</sub> | IUX_TP_CO | Internal temperature sensor coefficient                              | _    | 9.9  | —    | mV/°C |

|-----------------|-----------|----------------------------------------------------------------------|------|------|------|-------|

| V <sub>AM</sub> | IUX_TP    | Temperature sensor MUX_OUT output voltage (at $T_J = 165 \degree$ C) | 2.08 | 2.15 | 2.22 | V     |

### LDT: WHAT IS LDT ? HOW TO USE LDT? WHAT'S LDT ACCURACY ? HOW TO DO CALIBRATION ?

• Long duration timer(LDT), with an integrated oscillator. The timer is configurable by the SPI and can operate in normal mode and low-power mode. 2 time bases: 1s or 488uS, configured by SW register bits. The longest timer is 194 days with 1s time base.

|             | Osc freq | Osc period | Prescaler | Counter resolution | Max      | count    |                                                      |

|-------------|----------|------------|-----------|--------------------|----------|----------|------------------------------------------------------|

| Operation   | 32768 Hz | 30.52 µs   | 16 x 2048 | 1 s                | 4660 Hrs | 194 days | LONG_DURATION_TIMER register, MODE bit = 1 (default) |

| Calibration | 32768 Hz | 30.52 µs   | 16        | 488 µs             | 8192 s   | 2.28 Hrs | LONG_DURATION_TIMER register, MODE bit = 0           |

- Long duration timer(LDT) accuracy: Statistical analysis shows the ±5.0 % oscillator accuracy, After calibration, accuracy could achieve ±2.0 % from –20 °C to 85 °C temperature. Calibration method is in Page 71 of FS45/FS65 Datasheet V7.0.

- Long Duration Timer have 5 Modes, detailed description is in Page 72, Page 73 of FS45/FS65 Datasheet V7.0. Function 4 can be used as periodical wake-up system checking when system is in LPOFF mode.

- LDT function 5 principle(software flow) is shown in **Page 36** of NXP AN5238 V7.0.

- LDT diagnostic verify the correct operation of the LDT and wake-up by LDT in case it is used as a safety function. It is described in Page 37&Page38 of NXP AN5238 V7.0.

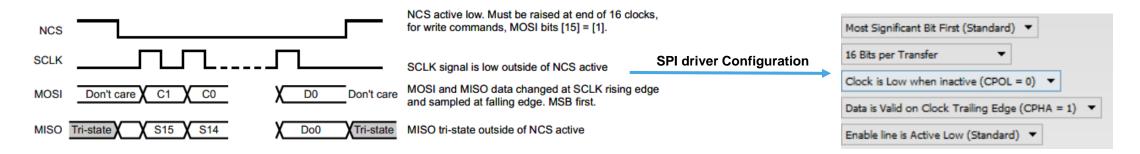

### SPI: WHAT'S FS45/FS65 SPI PROTOTYPE ? HOW TO CONFIGURE THE PARAMETER IN SOFTWARE?

#### • FS45/FS65 SPI Driver configuration.

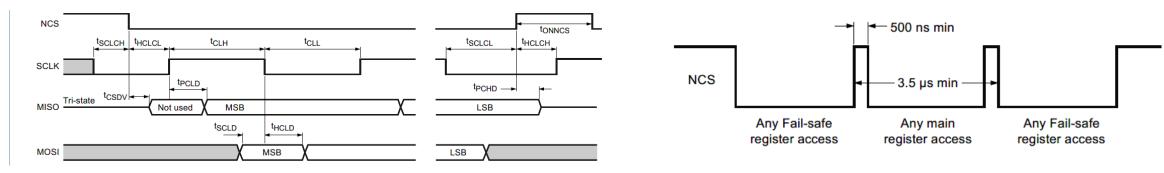

#### FS45/FS65 SPI Timing

- Detailed SPI timing, please refer to Page 22 of FS45/FS65 Datasheet.

- The minimum time between two NCS low sequences is defined by TONNCS= 500ns.

- Two consecutive accesses to the fail-safe registers must be done with a 3.5µs minimum NCS high time in between.

### IOS: WHAT FUNCTION IOO CAN SUPPORT AND HOW TO USE THE FUNCTION ?

- IOs have Multi-Function, "X" in below picture represents the function IO can support.

- IO0 Support Digital input wake up capability(default) and Analog input function.

Table 8. I/Os configuration

| l/O<br>number | Digital input wake-up<br>capability | Analog<br>input | Output gate<br>driver | VKAM | FCCU<br>monitoring | Ext. IC<br>monitoring |

|---------------|-------------------------------------|-----------------|-----------------------|------|--------------------|-----------------------|

| IO_0          | X                                   | Х               |                       |      |                    |                       |

| IO_2          | Х                                   |                 |                       |      | Х                  |                       |

| IO_3          | Х                                   |                 |                       |      | Х                  |                       |

| IO_4          | X                                   |                 | X                     |      |                    | X                     |

| IO_5          | X                                   | X               |                       | Х    |                    | Х                     |

### (1) IO0 can support Digital Input Function (Wake up IO)

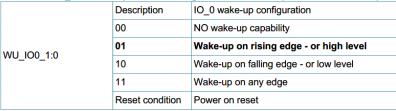

IO0 is wake up function by default, can wake up device when it is in LPOFF mode. Wake up source and wake up signals can be configured in INIT\_WU1 register as below.

#### Table 25. INIT\_WU1 description and configuration of the bits (default value in bold)

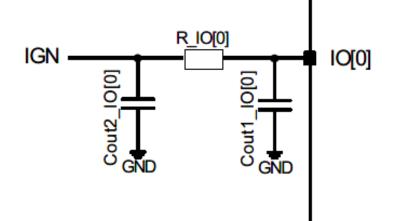

- IO0 pin max rating is 40V, IO0 is always recommended to connect to Ignition of the car.

- IO0 circuit is shown as below, Cout2\_IO[0] is used to against ESD GUN test up to ±8.0 kV, R\_IO[0] and a capacitor Cout1\_IO[0] to limit the current and the negative voltage during the high transient pulse on the line. Please see details in AN5238-5.5 IO\_0 ignition connection.

- Only IO0 Low to High transition can wake up device from Deep fail safe mode.

- Valid high/ low voltage: IO0 pin Voltage>2.6V = High, Voltage <2.1V = Low.

- Wake up signal delight time:

| t <sub>WU_GEN</sub> | General wake-up signal deglitch time (for any wake-up signal on IOs) | 60 | 70 | 80 | μs |

|---------------------|----------------------------------------------------------------------|----|----|----|----|

|                     |                                                                      |    |    |    |    |

#### (2) Analog Input Function

• IO0 is always used as wake up function, when used as analog input function, it support 19V max input.

### IOS: WHAT FUNCTION IO2&IO3 CAN SUPPORT AND HOW TO USE THE FUNCTION ?

- IOs have Multi-Function, "X" in below picture represents the function IO can support.

- IO2&IO3 Support Digital input wake up capability and FCCU function.

- IO2,IO3 are FCCU monitoring by default. The function can only be disabled in INIT\_FS mode.

| I/O<br>number | Digital input wake-up<br>capability | Analog<br>input | Output gate<br>driver | VKAM | FCCU<br>monitoring | Ext. IC monitoring |

|---------------|-------------------------------------|-----------------|-----------------------|------|--------------------|--------------------|

| IO_0          | X                                   | х               |                       |      |                    |                    |

| IO_2          | Х                                   |                 |                       |      | ×                  |                    |

| IO_3          | X                                   |                 |                       |      | Х                  |                    |

| IO_4          | Х                                   |                 | ×                     |      |                    | Х                  |

| IO_5          | X                                   | Х               |                       | Х    |                    | X                  |

(1) FCCU: when MCU detected error, it output unnormal FCCU/Fault signals to SBC IO2&IO3, SBC will reset MCU and assert FS0B=0 to make the system go to safe state. IO2/IO3 are FCCU safety pins by default, Polarity is PS=0 by default, If IO2/IO3 are not used, IO\_23\_FS bit must be configured to 0 in INIT\_FSSM register during INIT\_FS mode.

- Hardware connection is shown as the picture left for NXP or Non NXP MCU with PS=0.

- PS=0 Polarity means:

- (1) When IO[2]=**High**, IO[3] =**Low**, FCCU is normal. NO Reset toggled and FS0B is High. In this case, MCU should output **FCCU\_F[1]=Low** and **FCCU\_F[0]=High when MCU is normal**.

- (2) When IO[2], IO[3] are other states, SBC will Reset MCU and assert FS0B =0.

- SBC IO2&IO3 FCCU monitoring function only valid in Normal\_WD phase(as soon as first good SBC watchdog refresh).

- If SBC monitored FCCU error, customer can read the fault in DIAG\_SF\_IOs register:IO\_23\_FAIL bit.

#### (2) IO2, IO3 used as digital input wake up capability

- Configure IO\_23\_FS=0 No safety related & configure IO2,IO3 wake up type in INIT\_WU1 register.

- Hardware connection is same with IO0 wake up circuit.

- IO2&IO3 pins are 8V at max, so wake up voltage in IO2 and IO3 must not exceed 8V.

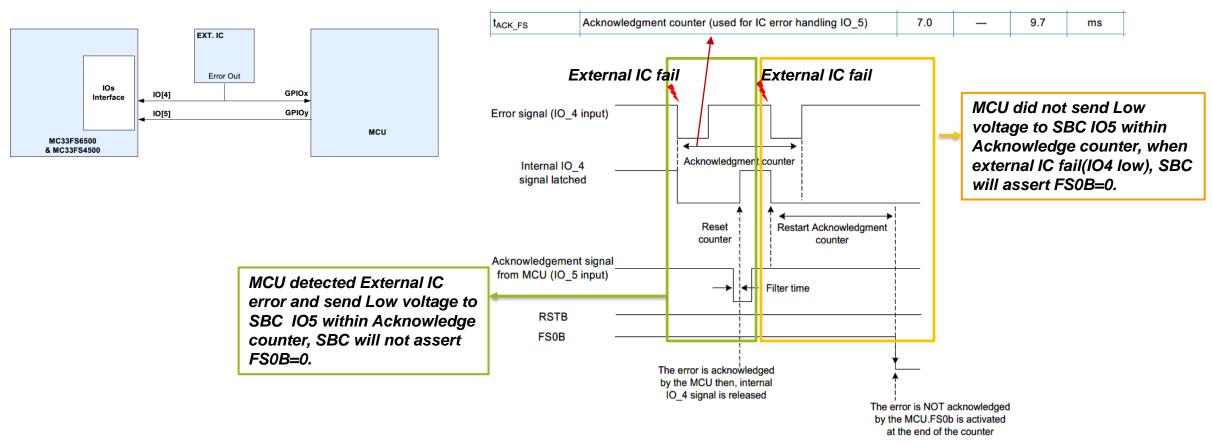

### IOS: WHAT FUNCTION 104&105 CAN SUPPORT AND HOW TO USE THE FUNCTION ?

- IOs have Multi-Function, "X" in below picture represents the function IO can support. **IO4 and IO5 are no wake up capability by default.**

- **IO4** Support **Digital input wake up capability, Analog input, output gate driver** function.

- **IO5** Support **Digital input wake up capability, Analog input, VKAM** function.

- IO4&IO5 can be configured as External IC monitoring function, it is disabled by default, it can be configured in INIT\_FSSM register during INIT\_FS mode.

#### Table 8. I/Os configuration

| l/O<br>number | Digital input wake-up<br>capability | Analog<br>input | Output gate<br>driver | VKAM | FCCU<br>monitoring | Ext. IC monitoring |

|---------------|-------------------------------------|-----------------|-----------------------|------|--------------------|--------------------|

| IO_0          | X                                   | X               |                       |      |                    |                    |

| IO_2          | Х                                   |                 |                       |      | Х                  |                    |

| IO_3          | X                                   |                 |                       |      | X                  |                    |

| IO_4          | Х                                   |                 | Х                     |      |                    | Х                  |

| IO_5          | Х                                   | Х               |                       | х    |                    | Х                  |

### (1) When IO4 is used as digital input wake up capability

- IO4 is used as no wake up by default, wake up function and type can be configured by writing INIT\_WU1 register, **WU\_IO4\_1:0.**

- Hardware connection is same with IO0 wake up circuit.

- 104

• IO4 pin is 40V max rating.

#### (2) When IO4 is used as output gate driver function

- Configure IO4 as no wake up capability in INIT\_WU1 register, WU\_IO4\_1:0 & configure IO4 as output gate driver by IO\_OUT\_AMUX register, IO\_OUT\_4\_EN, IO\_OUT\_4 bits.

- IO4 gate driver capability is shown as below.

| V <sub>IO4_OH</sub>     | High output level at $I_{IO4_OUT} = -2.0 \text{ mA}$ | V <sub>PRE</sub> – 1.5 | — | V <sub>PRE</sub> | V  |  |

|-------------------------|------------------------------------------------------|------------------------|---|------------------|----|--|

| V <sub>IO4_OL</sub>     | Low output level at I <sub>IO4_OUT</sub> = +2.0 mA   | 0.0                    | — | 1.0              | V  |  |

| V <sub>IO4_OUT_SK</sub> | Output current capability                            | 2.0                    | — | _                | mA |  |

| V <sub>IO4_OUT_SC</sub> |                                                      | —                      | — | -2.0             |    |  |

#### (1) When IO5 is used as digital input wake up capability

- IO5 is used as no wake up by default, wake up function and type can be configured by writing INIT\_WU1 register, **WU\_IO5\_1:0.**

- Hardware connection is same with IO0 wake up circuit.

- IO5 pin is 20V max rating.

#### (2) When IO5 is used as Analog Input function (20V Max)

Configure IO5 as no wake up capability in INIT\_WU1 register, WU\_IO5\_1:0 & configure IO5 as Analog Input by write IO\_OUT\_AMUX register AMUX\_2:0 Bits.

### (3) When IO5 is used as VKAM function.

- Configure IO5 as no wake up capability in INIT\_WU1 register& Configure MODE register VKAM\_EN =1, this register can only be written in Normal Mode(after write INIT\_INT register).

- Hardware connection is shown as —

- FS6504LAE&FS6514LAE IO5 is VKAM on by default.

220 nF

GND

### IOS: WHAT FUNCTION 104&105 CAN SUPPORT AND HOW TO USE THE FUNCTION ?

### IO4&IO5 used as External IC monitoring Function (Safety Function)

- IO4,IO5 are no wakeup capability by default and not safety related function by default, need configure INIT\_FSSM Register IO\_45\_FS=1 to active external sensor monitoring function.

- Hardware Connection.

NC

104&105

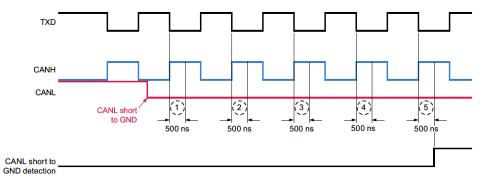

## CAN: HOW CANH/CANL SHORT TO BAT/GND DETECTED

CAN Diagnose function : CANH/CANL short to BATT/GND did not turn off CAN Transceiver.

#### Trigger condition:

1. CANL short to GND : VCANL pin voltage < 0.5V and 500 ns after TXD is activated low, and five consecutive times. 0.5V is not threshold, the threshold is within 0V~0.5V, when CAN BUS short to GND, CANL short to GND may not reported as CANL did not low enough for diagnose due to voltage gap between CAN BUS and CANL pin.

- 2. CANH short to BATT : VCANH pin voltage > 5.2V, 500 ns after TXD is activated low, and five consecutive times. 5.2V is not threshold, the threshold is within 0V~0.5V, when CAN BUS short to GND, CANL short to GND may not reported as CANL did not low enough for diagnose due to voltage gap between CAN BUS and CANL pin.

- 3. CANL short to BATT : ICANH > 75mA(typ), 500 ns after TXD is activated low, and five consecutive times. There is usually chock between CANH/CANL and CAN BUS, so when CAN BUS short to BATT, ICANL<75mA and CANL Short to BATT cannot reported due to chock impaction.

- 4. CANH short to GND : ICANL > 75mA(typ), 500 ns after TXD is activated low, and five consecutive times. There is usually chock between CANH/CANL and CAN BUS, so when CAN BUS short to BATT, ICANH<75mA and CANH Short to GND cannot reported due to chock impaction.

### CAN: FS45/FS65 CAN PHY WORK NORMALLY IN DEBUG MODE, BUT FAIL AFTER CHANGING TO NON-DEBUG MODE?

**Question:** Some customer find FS45/FS65 CAN PHY can work normally in debug mode, but after change to NON-Debug Mode, FS45/FS65 CAN PHY cannot work. **Answer:** This is mostly caused by unproper software configuration.

#### Check-List:

#### 1. CAN\_MODE\_1:0 bits in CAN\_LIN\_MODE Register.

- In debug mode, FS65 CAN PHY is normal mode by default. So CAN PHY can work without software configuration.

- In non-debug mode, FS65 CAN PHY is sleep/wake-up capability mode by default, need software configure CAN\_MODE\_1:0 = 11 in CAN\_LIN\_MODE register.

| Table 65. CAN_LIN_WOL       | DE description an | d configuration of the bits (default value in bold) |

|-----------------------------|-------------------|-----------------------------------------------------|

|                             | Description       | Configure the CAN mode                              |

|                             | 00                | Sleep/no wake-up capability                         |

| CAN_MODE_1:0 <sup>[1]</sup> | 01                | Listen only                                         |

| CAN_MODE_1.0                | 10                | Sleep/wake-up capability                            |

|                             | 11                | Normal operation mode                               |

|                             | Reset condition   | Power on reset                                      |

|                             | 11                | Normal operation mode                               |

Table 65. CAN\_LIN\_MODE description and configuration of the bits (default value in bold)

#### 2. FS1B\_CAN\_IMPACT bits in INIT\_FAULT Register.

- In debug mode, FS65 CAN PHY can work without considering FS1B pin state.

- In non-debug mode, FS65 CAN PHY mode will change to sleep/RX only(determined by CAN\_DIS\_CFG bit in INIT\_WU2 register) when FS1B is Low, it is configured in FS1B\_CAN\_IMPACT bits in INIT\_FAULT Register.

|                 | Description     | Configure CAN behavior when FS1B is asserted low               | CAN_DIS_CFG | Description     | Define CAN behavior when FS1B is asserted low                        |  |  |  |

|-----------------|-----------------|----------------------------------------------------------------|-------------|-----------------|----------------------------------------------------------------------|--|--|--|

|                 | 0               | No effect                                                      |             | 0               | CAN in RX only mode (when FS1B_CAN_ IMPACT = 1 in INIT_FAULT         |  |  |  |

| FS1B_CAN_IMPACT | 1               | CAN in RX only or sleep mode when FS1B is asserted (depends on |             |                 | register)                                                            |  |  |  |

|                 | -               | CAN_DIS_CFG bit in INIT_WU2 register)                          |             | 1               | CAN in sleep mode (when FS1B_CAN_ IMPACT = 1 in INIT_FAULT register) |  |  |  |

|                 | Reset condition | Power on reset                                                 |             | Reset condition | Power on reset                                                       |  |  |  |

### FS45/FS65 STATE MACHINE AND MODES

# QUESTIONS

- State Machine: <u>How main state machine and Fail Safe state machine work ?</u>

- State Machine: <u>How FS45/FS65 state machine work with MCU ?</u>

- State Machine: <u>How to change main/fail safe machine state?</u>

- State Machine: <u>How state machine change when FS45/FS65 RSTB pin asserted to Low?</u>

- > LPOFF/DFS Mode: <u>How to enter LPOFF/DFS and how to config DFS?</u>

- > **DEBUG Mode:** <u>How to enter/exist Debug mode, what's special in debug mode ?</u>

### STATE MACHINE: HOW MAIN STATE MACHINE AND FAIL SAFE STATE MACHINE WORK ?

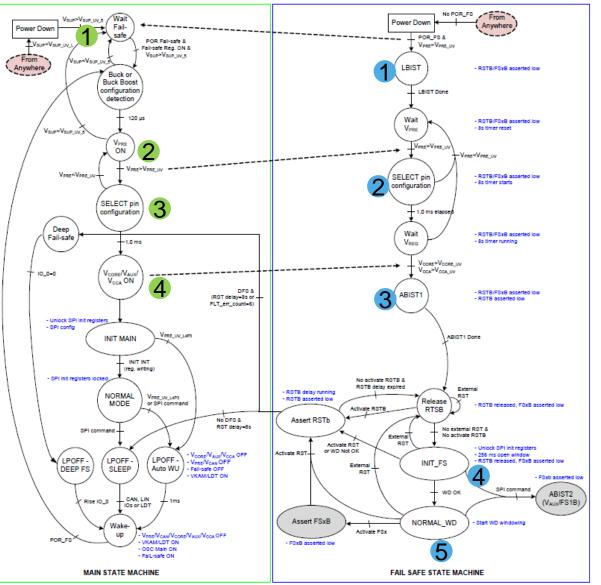

#### 2 State machine work in parallel.

- Main State Machine: Power Management;

- Fail Safe State Machine: Fail Safe Management.

NP

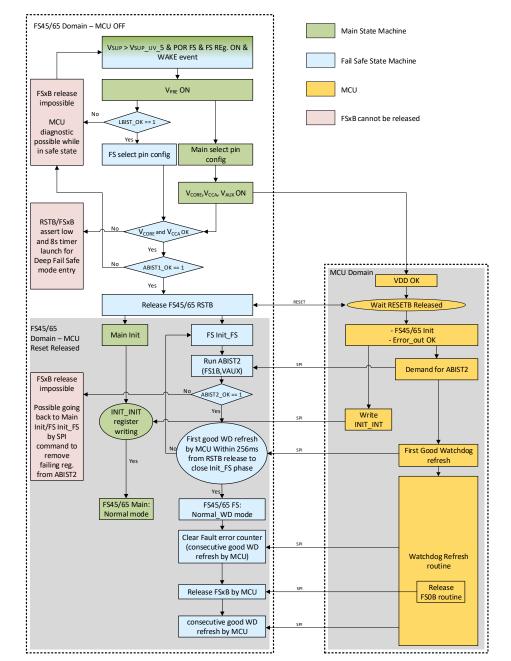

### STATE MACHINE: HOW FS45/FS65 STATE MACHINE WORK WITH MCU

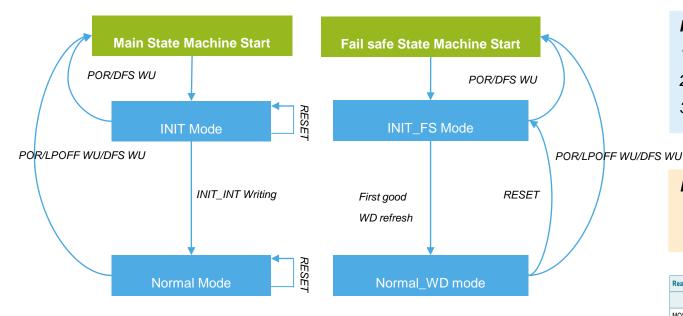

### STATE MACHINE: HOW TO CHANGE MAIN/FAIL SAFE MACHINE STATE?

#### Main State Machine (there are INIT and Normal Mode)

- Enter Normal Mode after SPI write INIT\_INT Register.

- Reset event in Normal Mode will not change Main State machine to INIT mode. All regulators can output normally.

- Re-enter INIT Mode after POR/wake-up from LPOFF or DFS

#### Fail safe State Machine (there are INIT\_FS and NORMAL\_WD mode)

- Enter INIT\_FS mode when Reset/POR/ wake-up from LPOFF or DFS.

- Enter NORMAL\_WD mode after first good watchdog refresh.

**Note:** Fail Safe State Machine did not work in LPOFF or DFS mode, so watchdog monitoring, OV/UV, FCCU monitoring did not work in LPOFF or DFS mode.

#### How state machine change when FS45/FS65 RSTB pin asserted to Low?

- 1. All power rails(Vpre/Vcore/Vaux/Vcca/Vcan) output normally.

- 2. Main state machine mode did not change.

- 3. Fail safe State machine change to "INIT\_FS" mode.

Note: MODE Register show main state machine mode, not Fail safe state machine mode. When read Mode register and shows "Normal mode", fail safe state machine may be in INIT\_FS mode or Normal\_WD mode.

| Read | lead  |       |       |       |       |       |       |         |         |          |       |      |      |        |      |       |

|------|-------|-------|-------|-------|-------|-------|-------|---------|---------|----------|-------|------|------|--------|------|-------|

|      | bit15 | bit14 | bit13 | bit12 | bit11 | bit10 | bit9  | bit8    | bit7    | bit6     | bit5  | bit4 | bit3 | bit2   | bit1 | bit0  |

| MOSI | 0     | 0     | 1     | 0     | 1     | 0     | 1     | 0       | 0       | 0        | 0     | 0    | 0    | 0      | 0    | 0     |

|      |       |       |       |       |       |       |       |         |         |          |       |      |      |        |      |       |

| MISO | SPI_G | WU_G  | CAN_G | LIN_G | 10_G  | VPRE  | VCORE | VOTHERS | VKAM_EN | RESERVED | RESER |      | INIT | NORMAL | DFS  | LPOFF |

|      |       |       |       |       |       | _G    | _G    | G       |         |          | VED   | ED   |      |        |      |       |

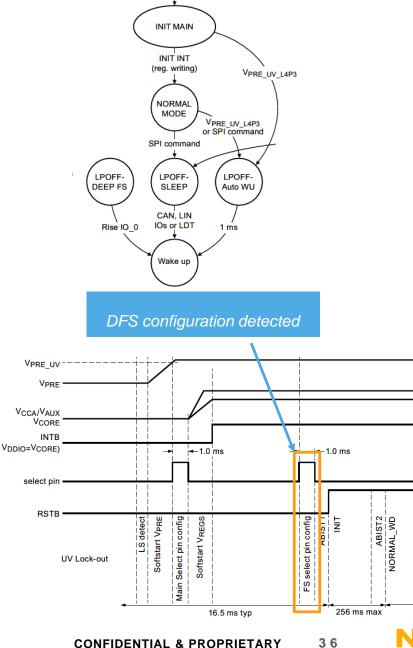

## LPOFF/DFS MODE: HOW TO ENTER LPOFF/DFS AND HOW TO CONFIG DFS

#### LPOFF Mode (all Regulators shut down, RSTB/FS0B/FS1B/INTB =0)

- LPOFF-Sleep mode can enter by SPI command(GO\_LPOFF bit =1 in MODE Register) and device can enter LPOFF-Sleep mode only when device is in Normal Mode;

- LPOFF\_AUTO\_WU can enter by SPI Command(LPOFF\_AUTO\_WU bit =1 in MODE Register) or VPRE<VPRE\_UV\_L4P3(both INIT and Normal Mode).</li>

- Device can be wake up by CAN/LIN/IO/LDT when in LPOFF-Sleep Mode.

- Fail safe registers configuration will lost to default value after wake up from LPOFF mode;

- Main registers configuration will not lost after wake up from LPOFF mode;

#### Deep Fail safe Mode(DFS, all Regulators shut down, RSTB/FS0B/FS1B/INTB =0)

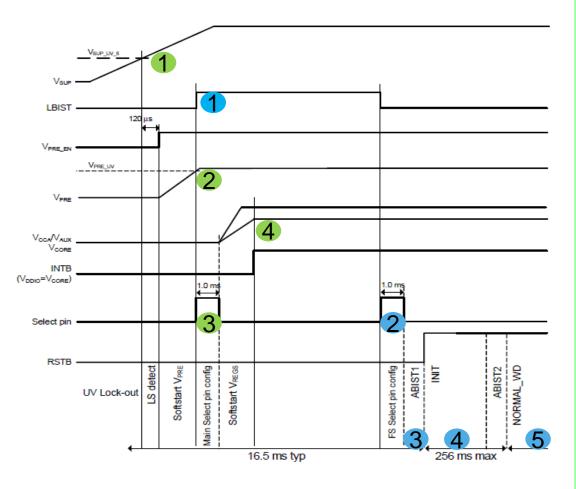

- DFS Enable/Disable is detected in **FS Select pin Config** phase and will not change if hardware connection change after FS Select pin Config phase.

- Fail safe registers configuration will lost to default value after wake up from DFS mode;

- Main registers configuration will not lost after wake up from DFS mode;

- DFS wake up only through IO0 go to low level(<2.1V) first, then go to high level(>2.6V);

|             | l behavior when DFS enabled/disabled:<br>Fault Error Counter = Max Value | RSTB low sustain >8s |

|-------------|--------------------------------------------------------------------------|----------------------|

| DFS Enable  | Enter DFS                                                                | Enter DFS            |

| DFS Disable | NO Enter DFS                                                             | Enter LPOFF          |

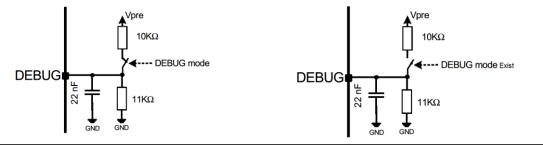

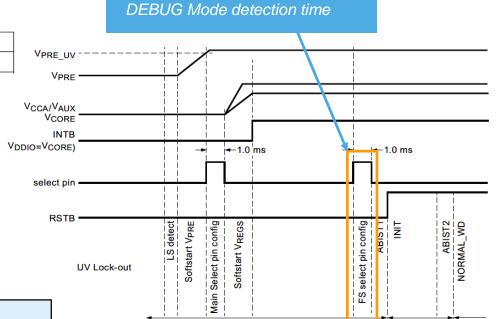

## DEBUG MODE: HOW TO ENTER/EXIST DEBUG MODE? WHAT IS SPECIAL FOR DEBUG MODE

#### How to enter DEBUG Mode?

• Debug pin voltage should be between 2.8V to 4.35V when device Power up.

| V <sub>DEBUG_IL</sub> | Low input voltage threshold  | 2.1  | 2.35 | 2.8  | V |  |

|-----------------------|------------------------------|------|------|------|---|--|

| V <sub>DEBUG_IH</sub> | High input voltage threshold | 4.35 | 4.6  | 4.97 | V |  |

- Debug mode is detected at FS select pin config phase, if debug pin voltage change after this phase, will not impact debug mode entry/exist.

- Recommended hardware connection

#### How to exist DEBUG Mode?

Leave Debug pin voltage <2.1V and Power up again.

#### What's special in DEBUG Mode?

1. Watchdog work in debug mode: watchdog can refresh any time and no watchdog window limitation.

| Mode  | NO watchdog refresh (timeout) | Right watchdog refresh | Wrong watchdog refresh        |  |  |  |

|-------|-------------------------------|------------------------|-------------------------------|--|--|--|

| Debug | no impaction                  | no impaction           | Action same as non-debug mode |  |  |  |

#### 2. DFS is disabled

fault error counter reach max value  $\rightarrow$  do not enter DFS.

RSTB asserted low >8s  $\rightarrow$  do not enter DFS or LPOFF.

16.5 ms typ

#### NXP INTERNAL USAGE

256 ms max

## **FS45/FS65 SAFETY FUNCTIONS**

## QUESTIONS

- Watchdog: What's Watchdog Content requirement? What's Watchdog refresh Time requirement ?

- Watchdog: What's the watchdog errors in INIT\_FS/NORMAL\_WD Phase?

- Watchdog: <u>How watchdog error counter works?</u>

- **Watchdog:** <u>How to Disable Periodic Watchdog ? How to change Watchdog Window time at Normal WD phase?</u>

- RESET: What's reset Trigger Source and how to Configure Trigger Source ?

- **FSOB/FS1B:** <u>How to release FSOB/FS1B, check list when FSOB/FS1B cannot release ?</u>

- **FS1B:** <u>How to configure FS1B delay time ? What's the behavior when device enter DFS/LPOFF/POR?</u>

- Fault error Counter: <u>How to increase/ decrease fault error counter value?</u>

- > ABIST1/ABIST2: What's the Check items?

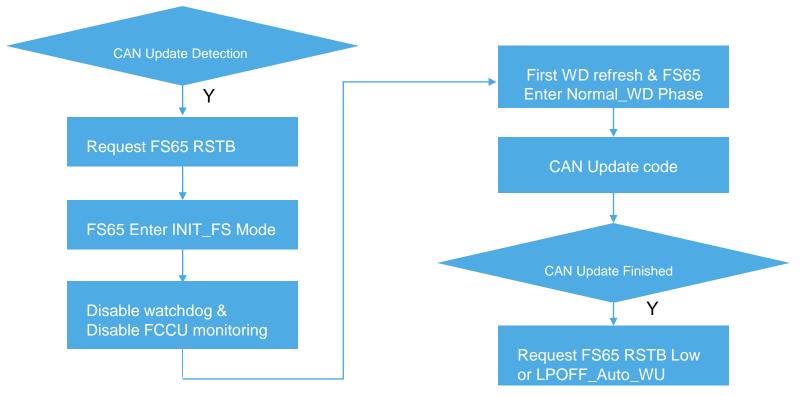

- How to do code update with CAN in the garage ?

- FS45,FS65 ASILB & FS45,FS65 ASIL D Compliant ?

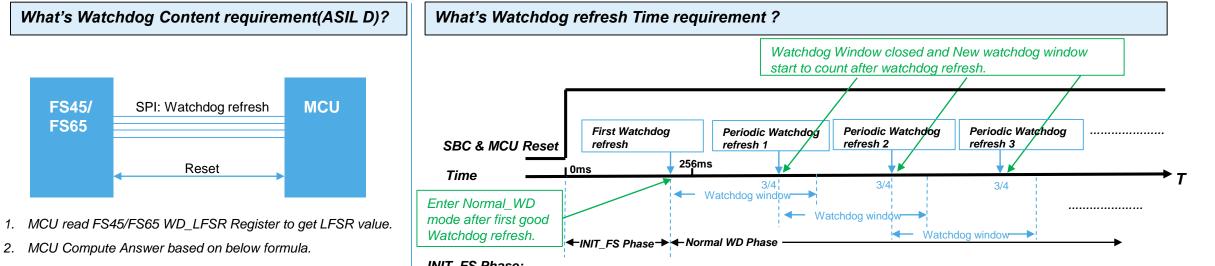

### WATCHDOG: WHAT'S WATCHDOG CONTENT REQUIREMENT? WHAT'S WATCHDOG REFRESH TIME REQUIREMENT ?

Watchdog refresh is conducted through SPI between MCU and FS45/FS65.

NOT

6

4

MCU Write the answer to FS45/FS65 WD\_ANSWER register.

Note: LFSR value changed every time WD\_ANSWER register

For example, LFSR is 0xB2, WD\_ANSWER is 0x4D.

WD answer[7:0]

aaa-037747

• FS45/FS65(ASIL D) integrated challenger watchdog mechanism, it requires right watchdog content and right watchdog refresh time.

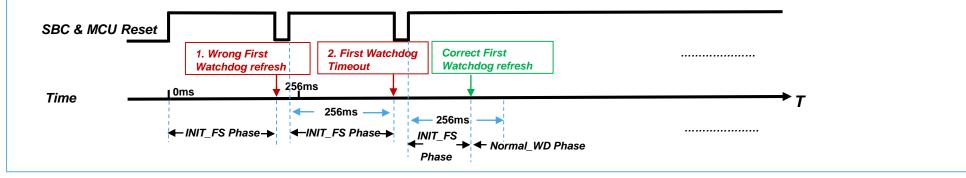

#### INIT FS Phase:

- 1. First watchdog must refresh within 256ms after Reset release to high & all fail safe INIT Registers configuration are finished.

- If first watchdog refresh correctly during 256ms, FS65 enter Normal\_WD phase directly(do not wait for 256ms counter end). Periodical watchdog refresh is needed and watchdog error/refresh counter start to work in Normal\_WD Phase.

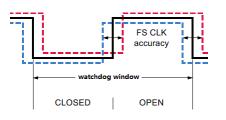

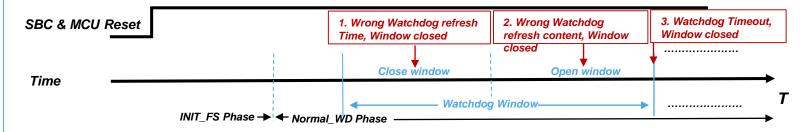

#### Normal WD Phase:

- 1. After First watchdog refresh finished, MCU must refresh watchdog periodical, Periodical watchdog window has close window and Open window, watchdog must be refreshed at open window and highly recommended to Periodical refresh at 3/4 of watchdog window as FS CLK accuracy is 10%.

- 2. New watchdog window counter starts at the time wrong watchdog refresh or good watchdog refresh or watchdog window timeout.

|     |                |          | Window |

|-----|----------------|----------|--------|

|     |                | CLOSED   | OPEN   |

|     | BAD key        | WD_NOK   | WD_NOK |

| SPI | GOOD key       | WD_NOK   | WD_OK  |

|     | None (timeout) | No_issue | WD_NOK |

is written or watchdog timeout.

1.

З.

4.

LFSR OUT[7:0]

## WATCHDOG: WHAT'S THE WATCHDOG ERRORS IN INIT\_FS/NORMAL\_WD PHASE?

#### What's the watchdog errors in INIT FS Phase?

Watchdog errors at INIT\_FS Phase: there are 2 kinds of watchdog errors at INIT\_FS phase, Reset will asserted to low when errors happen.

Error 1: If first watchdog refresh not Correct, FS45/FS65 Reset directly, FS45/FS65 enter INIT\_FS mode again and request first correct watchdog refresh within 256ms.

Error 2: If first watchdog did not refresh within 256ms, FS45/FS65 Reset directly, FS45/FS65 enter INIT\_FS mode again and request first correct watchdog refresh within 256ms.

#### What's the watchdog errors in Normal\_WD Phase ?

Watchdog Errors at Normal WD Phase: there are 3 kinds of watchdog errors at Normal\_WD phase.

*Error1:* watchdog refresh at close window. WD\_BAD\_TIMING =1 in WD\_ANSWER register.

*Error2:* watchdog refresh at open window but watchdog answer is wrong; WD\_BAD\_DATA =1 in WD\_ANSWER register.

*Error3:* watchdog did not refresh at whole watchdog window, watchdog timeout. WD\_BAD\_TIMING =1 in WD\_ANSWER register.

Note: In NORMAL\_WD mode, one watchdog error did not cause RSTB/FS0B Asserted to low, When WD error Counter reach max value, RSTB&FS0B react can be configured by WD\_IMPACT\_1:0 bits.

NP

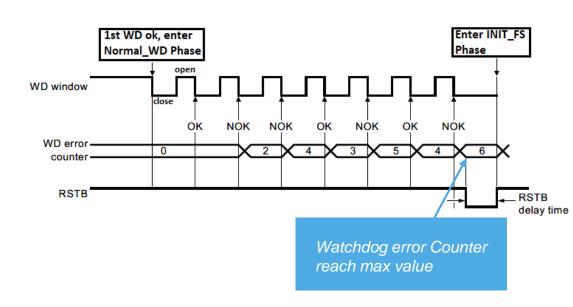

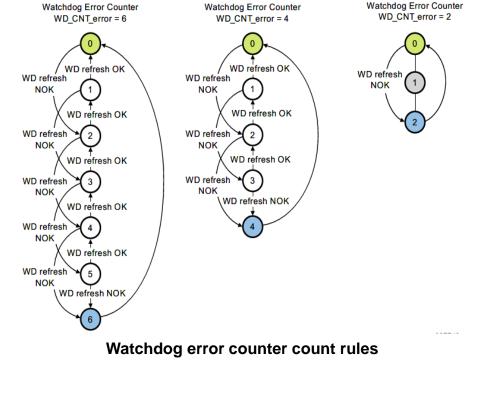

## WATCHDOG: HOW WATCHDOG ERROR COUNTER WORKS?

#### How watchdog error Counter works?

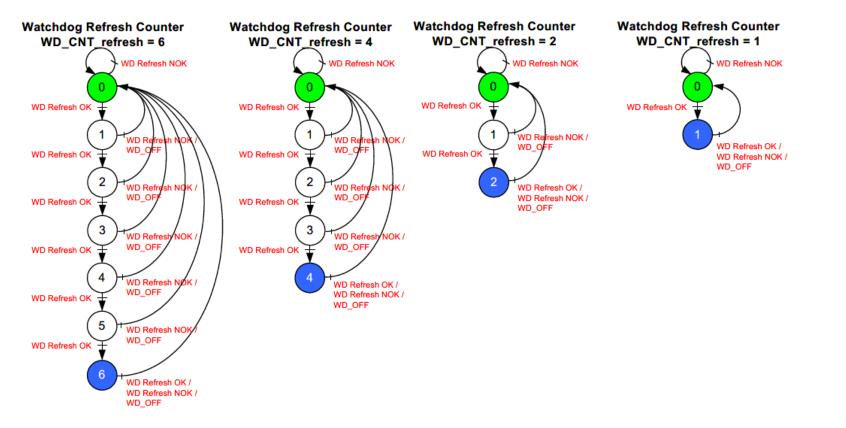

Watchdog error counter: work in Normal\_WD phase. Max value[2 or 4 or 6(default)] is configured in WD\_CNT\_ERR\_1:0 bits, INIT\_WD\_CNT register.

- Wrong watchdog: Counter +2; right watchdog: Counter-1,

- When Watchdog error Counter reach max value, safety action by default : 1. fault error counter +1; 2. RSTB asserted to Low;

- Watchdog error counter max value can impact NONE/RSTB/FS0B/RSTB&FS0B, it is configured by WD\_IMPACT\_1:0 bits in INIT\_SF\_IMPACT Register.

If WD\_IMPACT\_1:0 = 01 configured to impact RSTB when watchdog error Counter reach max value,

FS65 will enter INIT\_FS mode after RSTB released to high.

• If WD\_IMPACT\_1:0 = 00/10 did not impact RSTB, FS65 will still at Normal\_WD phase when

• If WD\_IMPACT\_1:0 = 00 did not impact RSTB or FS0B, fault error counter will not increase, when watchdog error counter reach max value.

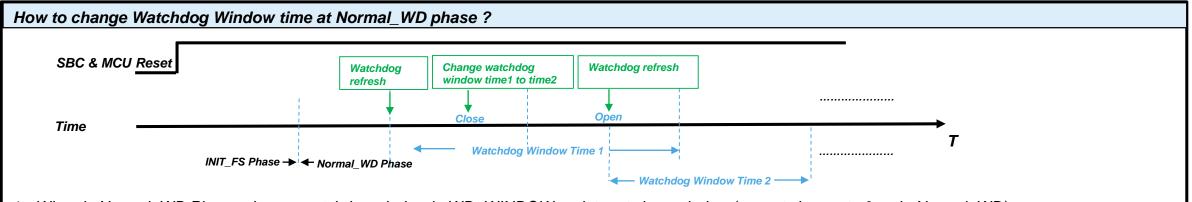

## WATCHDOG: HOW TO DISABLE PERIODIC WATCHDOG ? HOW TO CHANGE WATCHDOG WINDOW TIME AT NORMAL\_WD PHASE ?

#### How to Disable Periodic Watchdog?

- Periodic watchdog can be disabled by configuring WD\_WINDOW\_3:0 = 0000 in WD\_WINDOW Register (only can be configured in INIT\_FS phase)

- First watchdog refresh in INIT\_FS phase(within 256ms) is needed and period watchdog refresh is not needed when watchdog window is 0.

- When watchdog window is 0, watchdog can be refreshed without time limitation(except first watchdog refresh). Fault error counter will be decreased when watchdog refresh counter reach max value.

- When watchdog window is 0, bad watchdog refresh will increase watchdog error Counter and increase fault error counter when watchdog error counter reach max value.

- 1. When in Normal\_WD Phase, change watchdog window in WD\_WINDOW register at close window.(cannot change to 0ms in Normal\_WD)

- 2. Watchdog refresh according to the watchdog window time before change in open window.

- 3. After watchdog refresh, new watchdog window will be valid, need to refresh watchdog according to new watchdog time window.

- 4. If watchdog refresh is not correct or watchdog time out, new watchdog window time will also be valid in the coming window.

## RESET: WHAT'S RESET TRIGGER SOURCES AND HOW TO CONFIGURE TRIGGER SOURCE?

#### How to configure RSTB activation or non-activation for the faults?

The activation of RSTB depends on the fail-safe state machine configuration performed during the INIT\_FS phase.

The following faults impact on RSTB activation can be configured:

- Watchdog error counter = max value (6 by default) // INIT\_SF\_IMPACT Register: WD\_IMPACT\_1:0

- VCORE, VCCA, VAUX undervoltage

INIT\_VCORE\_OVUV\_IMPACT/INIT\_VCCA\_OVUV\_IMPACT/INIT\_VAUX\_OVUV\_IMPACT Register

- VCORE, VCCA, VAUX overvoltage

INIT\_VCORE\_OVUV\_IMPACT/ INIT\_VCCA\_OVUV\_IMPACT/ INIT\_VAUX\_OVUV\_IMPACT Register

- FCRBM follows VCORE configuration INIT\_VCORE\_OVUV\_IMPACT Register, same configuration with Vcore

- IO\_23 error detection (FCCU)

INIT\_FSSM Register: IO\_23\_FS bit

Fault error counter level

INIT\_FAULT Register: FLT\_ERR\_IMP\_1:0 bits

The following faults impact on RSTB activation cannot be configured:

- VPRE overvoltage

- Watchdog refresh not OK or watchdog timeout during INIT phase

- FS0B short to high

- RSTB pulse requested by SPI

#### How to check RSTB Source when RSTB happen ?

- 1. Check RSTB low duration.

- If RSTB low duration is not close to configured RSTB low duration INIT\_FSSM RSTB\_DURATION bit, it is most probability External Reset. Reading DIAG\_SF\_IOs register RSTB\_EXT bit to confirm whether it is an external REST.

- If RSTB low duration is close to configured RSTB low duration, it is most probability caused by SBC.

- 2. Check if the Reset happen once or frequently

- If once, please check regulators output when RSTB low with oscilloscope, please also check if there is OV/UV flag reported.

- If Reset happen frequently, Please check if the time cycle is related to watchdog and watchdog error counter max value.

#### 3. Check when RSTB Happen

- If RSTB asserted to low as soon as first right watchdog refresh, it is mostly caused by FCCU error, please check DIAG\_SF\_IOs register, IO\_23\_FAIL bit.

- FCCU Error can be confirmed by configuring INIT\_FSSM: IO\_23\_FS bit =0 to see if the failure removed.

### FS0B/FS1B: HOW TO RELEASE FS0B/FS1B, CHECK LIST WHEN FS0B/FS1B CANNOT RELEASE

#### How to release FS0B/FS1B?

Fault is removed

- First, SPI Read BIST Register : LBIST OK& ABIST1 OK must be "1", otherwise, FS0B/FS1B cannot be released.

- ABIST2\_FS1B\_OK=1 if part number with FS1B

SPI Write BIST Register: ABIST2\_FS1B=1

- ABIST2\_VAUX\_OK=1 except if VAUX\_FS\_OV\_1:0=VAUX\_FS\_UV\_1:0="00" ----> SPI Write BIST Register, ABIST2\_VAUX=1

- 7\* successful continuous watchdog refresh can clear Fault error counter from 1 to 0 Fault error counter must be at '0' —

- Close the S1 switch if FS1B backup delay was engaged (FS1B\_DLY\_DRV bit = 1) -> SPI Write SF\_OUTPUT\_REQUEST register: FS1B\_DLY\_REQ =0

- RELEASE\_FSxB register must be filled with the right value

| 1. Read Latest LFSR value(WD_LFSR register).              |                       | WD_LFSR_7:0      | b7 | b6 | b5 | b4        | b3 | b2 | b1        | 60 |

|-----------------------------------------------------------|-----------------------|------------------|----|----|----|-----------|----|----|-----------|----|

| 2. Calculate release command based on Rules in the right. | Release FS0B          | RELEASE_FSxB_7:0 | 0  | 1  | 1  | b0        | b1 | b2 | b3        | b4 |

|                                                           | Release FS1B          | RELEASE_FSxB_7:0 | 1  | 1  | 0  | b3        | b4 | b5 | b6        | b7 |

| 3. SPI write release command to RELEASE_FSxB register.    | Release FS0B and FS1B | RELEASE_FSxB_7:0 | 1  | 0  | 1  | <b>b0</b> | b1 | b2 | <b>b6</b> | b7 |

What's the Check List when FS0B/FS1B cannot be released?

#### 1. Check LBIST ABIST1, ABIST2 result in BIST register

If LBIST fail, there is something wrong in the Chip.

If ABIST1 fail, please check if Vpre, Vcore, Vcca, Vaux regulators output stable before RSTB release to high.

#### 2. Check fault error counter value by reading DIAG\_FS\_ERR register, FLT\_ERR\_2:0 bits

If fault error counter value is not 0, please check if FCCU report error by reading IO 23 FAIL bit.

Please check if there is watchdog error by reading WD BAD TIMING/WD BAD DATA bits.

Please check if other faults, like UV/OV:

#### 3. Check release command and release time

Release command should align with the rules.

The RELEASE FSxB write command must be done after the WD LFSR read command, within the same WD period.

#### NXP INTERNAL USAGE

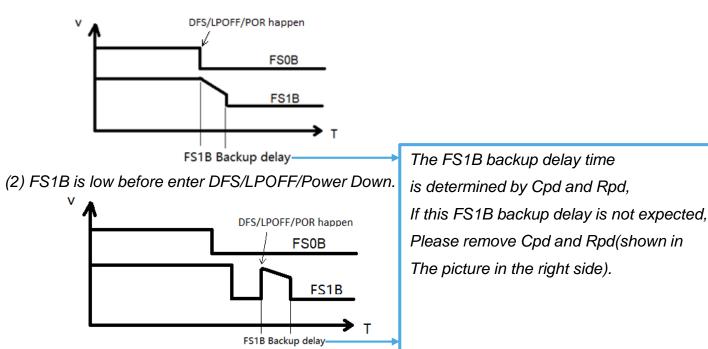

## FS1B: HOW TO CONFIGURE FS1B DELAY TIME ? WHAT'S THE BEHAVIOR WHEN DEVICE ENTER DFS/LPOFF/POR?

#### How to configure FS1B delay time ?

- FS1B delay mode can be configured in software by writing INIT\_SF\_IMPACT register, TDLY\_TDUR =0.

- FS1B delay time can be configured in INIT\_FS1B\_TIMING register, FS1B\_TIME\_3:0 bits and INIT\_SUPERVISOR register: FS1B\_TIME\_RANGE bit, longest delay time is 3.15s.

- FS1B Back up delay is determined by External Rpd and Cpd in Vpu\_fs pin. When Switch S1 open, Cpd discharge through Rpd, FS1B will be asserted to low when Vpu\_fs voltage decreased to 3.2V from ~5.4V. Switch S1 is controlled by FS1B\_DLY\_REQ bit(open by default) in SF\_OUTPUT\_REQUEST register.

#### What's FS1B behavior when device enter DFS/LPOFF/POR?

#### (1) FS1B is high before enter DFS/LPOFF/Power Down.

## FAULT ERROR COUNTER: HOW TO INCREASE/ DECREASE FAULT ERROR COUNTER VALUE?

#### How to increase/ decrease fault error counter value?

- Fault error Counter value reach max value, device enter DFS mode, all regulators shut down. Max value can be 2,4,6(default) by SPI Writing INIT\_FAULT Register, FLT\_ERR\_FS bit.

- Fault error counter increase: fault error counter is 1 by default when powerup or wakeup from LPOFF, fault error counter increase every time RSTB, FS0B asserted to low.

- Fault error Counter decrease: Fault error Counter value decrease when watchdog refresh counter reach max value. Watchdog error counter max value can be configured to 2,4,6(default) by writing INIT\_WD\_CNT Register: WD\_CNT\_RFR\_1:0 bits.

## ABIST1/ABIST2:WHAT'S THE CHECK ITEMS

|                                                                     |                                                               | AB                                                                                          | IST1                                                                      | ABIST2 |           | IST2                                                    |                                                                                             |  |

|---------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------|-----------|---------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

|                                                                     | automatic                                                     |                                                                                             |                                                                           |        | on demand |                                                         | Comment                                                                                     |  |

|                                                                     | ٥V                                                            | UV                                                                                          | OK/NOK                                                                    | ٥v     | UV        | OK/NOK                                                  |                                                                                             |  |

| Vpre                                                                | x                                                             |                                                                                             |                                                                           |        |           |                                                         | UV from cascaded regulators (Vcore, Vcca, Vaux)                                             |  |

| Vcore                                                               | x                                                             | x                                                                                           |                                                                           |        |           |                                                         | Both UV/OV checked                                                                          |  |

| Vcca                                                                | x                                                             | x                                                                                           |                                                                           |        |           |                                                         | Both UV/OV checked                                                                          |  |

| Vaux                                                                |                                                               |                                                                                             |                                                                           | х      | х         |                                                         | Both UV/OV checked                                                                          |  |